Download - Spansion

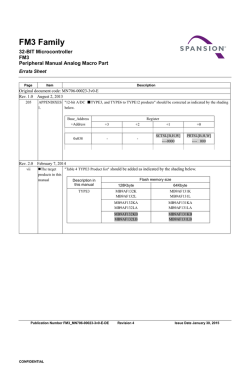

FM3 Family 32-BIT Microcontroller FM3 Peripheral Manual Communication Macro Part Errata Sheet Page Item Description Original document code: MN706-00024-3v0-E Rev. 1.0 August 2, 2013 581 Rev. 2.0 vii APPENDIXES "12-bit A/DC ■TYPE3, and TYPE6 to TYPE12 products" should be corrected as indicated by the shading 1. below. Base_Address +Address +3 +2 Register +1 +0 0x038 - - SCTSL[B,H,W] ----0000 PRTSL[B,H,W] ---- 000 February 7, 2014 The target "Table 4 TYPE3 Product list" should be added as indicated by the shading below. products in this Flash memory size manual Description in this manual 128Kbyte 64Kbyte TYPE3 Publication Number FM3_MN706-00024-3v0-E-DE CONFIDENTIAL MB9AF132K MB9AF132L MB9AF131K MB9AF131L MB9AF132KA MB9AF132LA MB9AF131KA MB9AF131LA MB9AF132KB MB9AF132LB MB9AF131KB MB9AF131LB Revision 4 Issue Date January 30, 2015 E R R A T A Page viii Item The target products in this manual Description "Table 7 TYPE6 Product list" should be added as indicated by the shading below. Description in this manual TYPE6 viii The target products in this manual CONFIDENTIAL Flash memory size 256Kbyte 128Kbyte 64Kbyte MB9AFB44L MB9AFB44M MB9AFB44N MB9AFB44LA MB9AFB44MA MB9AFB44NA MB9AFB44LB MB9AFB44MB MB9AFB44NB MB9AFA44L MB9AFA44M MB9AFA44N MB9AFA44LA MB9AFA44MA MB9AFA44NA MB9AFA44LB MB9AFA44MB MB9AFA44NB MB9AF344L MB9AF344M MB9AF344N MB9AF344LA MB9AF344MA MB9AF344NA MB9AF344LB MB9AF344MB MB9AF344NB MB9AF144L MB9AF144M MB9AF144N MB9AF144LA MB9AF144MA MB9AF144NA MB9AF144LB MB9AF144MB MB9AF144NB MB9AFB42L MB9AFB42M MB9AFB42N MB9AFB42LA MB9AFB42MA MB9AFB42NA MB9AFB42LB MB9AFB42MB MB9AFB42NB MB9AFA42L MB9AFA42M MB9AFA42N MB9AFA42LA MB9AFA42MA MB9AFA42NA MB9AFA42LB MB9AFA42MB MB9AFA42NB MB9AF342L MB9AF342M MB9AF342N MB9AF342LA MB9AF342MA MB9AF342NA MB9AF342LB MB9AF342MB MB9AF342NB MB9AF142L MB9AF142M MB9AF142N MB9AF142LA MB9AF142MA MB9AF142NA MB9AF142LB MB9AF142MB MB9AF142NB MB9AFB41L MB9AFB41M MB9AFB41N MB9AFB41LA MB9AFB41MA MB9AFB41NA MB9AFB41LB MB9AFB41MB MB9AFB41NB MB9AFA41L MB9AFA41M MB9AFA41N MB9AFA41LA MB9AFA41MA MB9AFA41NA MB9AFA41LB MB9AFA41MB MB9AFA41NB MB9AF341L MB9AF341M MB9AF341N MB9AF341LA MB9AF341MA MB9AF341NA MB9AF341LB MB9AF341MB MB9AF341NB MB9AF141L MB9AF141M MB9AF141N MB9AF141LA MB9AF141MA MB9AF141NA MB9AF141LB MB9AF141MB MB9AF141NB "Table 9 TYPE8 Product list" should be added as indicated by the shading below. Description in this manual TYPE8 2 S H E E T Flash memory size 512Kbyte 384Kbyte 256Kbyte MB9AF156M MB9AF156N MB9AF156R MB9AF156MA MB9AF156NA MB9AF156RA MB9AF155M MB9AF155N MB9AF155R MB9AF155MA MB9AF155NA MB9AF155RA MB9AF154M MB9AF154N MB9AF154R MB9AF154MA MB9AF154NA MB9AF154RA FM3_MN706-00024-3v0-E-DE4, January 30, 2015 E R R A T A Page Item 410 CHAPTER 3-2: USB Host 5.2. Host Interrupt Register (HIRQ) S H E E T Description "Summary" should be added as indicated by the shading below. The Host Interrupt Register (HIRQ) indicates the USB host interrupt request flag. A host interrupt can occur by setting the interrupt enable bit of the Host Control Register (HCNT0 or HCNT1), excluding the TCAN bit. Host Interrupt Register (HIRQ) should be accessed with a byte access instruction. "[bit7] TCAN" should be added as indicated by the shading below. If this bit is set to "1", it means that token sending is canceled based on the setting of the CANCEL bit of Host Control Register 1 (HCNT1). When this bit is "0", it means that token sending is not canceled. If this bit is written with "0", it is set to "0". However, if this bit is written with "1", its value is ignored. A read-modify-write access reads the bit as "1". 411 "[bit5] RWKIRQ" should be added as indicated by the shading below. When the RWKIRE bit of Host Control Register 0 (HCNT0) is "1", an interrupt occurs if this bit is set to "1". A read-modify-write access reads the bit as "1". "[bit4] URIRQ" should be added as indicated by the shading below. When the URIRE bit of Host Control Register 0 (HCNT0) is "1", an interrupt occurs if this bit is set to "1". A read-modify-write access reads the bit as "1". 412 "[bit3] CMPIRQ" should be added as indicated by the shading below. When the CMPIRE bit of Host Control Register 0 (HCNT0) is "1", an interrupt occurs if this bit is set to "1". A read-modify-write access reads the bit as "1". Notes of "[bit3] CMPIRQ" should be added as indicated by the shading below. ・This bit is set to the initial value when "1" is set to the RST bit of the UDC Control Register (UDCC). ・This bit is not set to "1" even if the TCAN bit of the Host Interrupt Register (HIRQ) changes to "1". ・Take the following steps when this bit is set to “1” by finishing IN token or Isochronous IN token. 1) Read HS bit of Host Error Status Register (HERR), then set CMPIRQ bit to “0”. 2) Set DRQIE bit of EPn Status Register (EPnS) (n=1 or 2) to “1” if HS bit of Host Error Status Register (HERR) is equal to “00” and wait until DRQ bit changes to “1”. Finish the IN token processing if HS bit is not equal to “00”. 3) Read the received data if DRQ bit of EPn Status Register (EPnS) changes to “1”. "[bit2] CNNIRQ" should be added as indicated by the shading below. When the CNNIRE bit of Host Control Register 0 (HCNT0) is "1", an interrupt occurs if this bit is set to "1". A read-modify-write access reads the bit as "1". January 30, 2015, FM3_MN706-00024-3v0-E-DE4 CONFIDENTIAL 3 E R R A T A Page 412 Item S H E E T Description CHAPTER 3-2: Notes of "[bit2] CNNIRQ" should be corrected as indicated by the shading below. USB Host 5.2. Host (Error) Interrupt ・This bit is set to the initial value when "1" is set to the RST bit of the UDC Control Register (UDCC). Register (HIRQ) (Correct) ・This bit is not initialized even if "1" is set to the RST bit of the UDC Control Register(UDCC). 413 "[bit1] DIRQ" should be added as indicated by the shading below. When the DIRE bit of Host Control Register 0 (HCNT0) is "1", an interrupt occurs if this bit is set to "1". A read-modify-write access reads the bit as "1". 413 CHAPTER 3-2: Notes of "[bit1] DIRQ" should be corrected as indicated by the shading below. USB Host 5.2. Host (Error) Interrupt ・This bit is set to the initial value when "1" is set to the RST bit of the UDC Control Register (UDCC). Register (HIRQ) (Correct) ・This bit is not initialized even if "1" is set to the RST bit of the UDC Control Register(UDCC). "[bit0] SOFIRQ" should be added as indicated by the shading below. When the SOFIRE bit of Host Control Register 0 (HCNT0) is "1", an interrupt occurs if this bit is set to "1". A read-modify-write access reads the bit as "1". 414 CHAPTER 3-2: USB Host 5.3.Host Error Status Register (HERR) 427 "Summary" should be added as indicated by the shading below. The Host Error Status Register (HERR) indicates whether or not an error occurs while sending or receiving data in the host mode. Host Error Status Register (HERR) should be accessed with a byte access instruction. "[bit9:8] HS" should be added as indicated by the shading below. These flags are set to "NULL" when no handshake occurs due to an error or when a SOF token has been ended with the TKNEN bit of the Host Token Endpoint Register (HTOKEN). These bits are updated when sending or receiving has been ended. HS bits change values "11" under the following condition. However, if HS bits are written except the following conditions, the values are ignored. -HS bits indicate values except "11" and write the value "11" to HS bits. 4 CONFIDENTIAL FM3_MN706-00024-3v0-E-DE4, January 30, 2015 E R R A T A Page S H E E T Item Description 437 CHAPTER 3-2: Notes of " [bit6:4] TKNEN" should be added as indicated by the shading below. USB Host 5.10. Host Token ・When the device is disconnected (CSTAT of HSTATE = "0"), token sending is not performed even if data Endpoint is written to this bit. Register ・Read the value of TKNEN bit if a new value is written in it .Continue writing in this bit until a retrieved (HTOKEN) value equals a new value written in.During this checking process, it is needed to prevent any interrupt. ・Take the following steps when CMPIRQ bit of Host Interrupt Register (HIRQ) is set to “1” by finishing IN token or Isochronous IN token. 1) Read HS bit of Host Error Status Register (HERR), then set CMPIRQ bit to “0”. 2) Set DRQIE bit of EPn Status Register (EPnS) (n=1 or 2) to “1” if HS bit of Host Error Status Register (HERR) is equal to “00” and wait until DRQ bit changes to “1”. Finish the IN token processing if HS bit is not equal to “00”. 3) Read the received data if DRQ bit of EPn Status Register (EPnS) changes to “1”. 547 CHAPTER 6-3: CEC Transmission 5.3. Arbitration Lost Detection "How to detect arbitration lost" should be deleted as indicated by the shading below. CHAPTER 6-3: CEC Transmission 5.3. Arbitration Lost Detection "Figure 5-3 Arbitration Lost Detection Period" should be corrected as below. 547 Data on the bus is sampled with about 32 kHz cycle per bit during the following detection period and compared to the transmission output. If any difference is continuously detected in 2 samplings, an arbitration lost will be detected. If the arbitration lost is detected, IBR of the TXSTS register becomes "1". 10 cycle Sampling at about 32kHz cycle Detection period Start of next bit “0” output period 583 “1” output period APPENDIXES "CR Trim" should be corrected as indicated by the shading below. A. Register Map Base_Address +Address +3 +2 +1 +0 0x008 - - - MCR_TTRM[B,H,W] --011111 January 30, 2015, FM3_MN706-00024-3v0-E-DE4 CONFIDENTIAL Register 5 E R R A T A Page 628 Item Description APPENDIXES "Table 4 TYPE3 Product list" should be added as indicated by the shading below. D Product TYPE Flash memory size List Description in this manual 128Kbyte 64Kbyte TYPE3 629 S H E E T MB9AF132K MB9AF132L MB9AF131K MB9AF131L MB9AF132KA MB9AF132LA MB9AF131KA MB9AF131LA MB9AF132KB MB9AF132LB MB9AF131KB MB9AF131LB APPENDIXES "Table 7 TYPE6 Product list" should be added as indicated by the shading below. D Product TYPE Flash memory size List Description in this manual 256Kbyte 128Kbyte 64Kbyte TYPE6 6 CONFIDENTIAL MB9AFB44L MB9AFB44M MB9AFB44N MB9AFB44LA MB9AFB44MA MB9AFB44NA MB9AFB44LB MB9AFB44MB MB9AFB44NB MB9AFA44L MB9AFA44M MB9AFA44N MB9AFA44LA MB9AFA44MA MB9AFA44NA MB9AFA44LB MB9AFA44MB MB9AFA44NB MB9AF344L MB9AF344M MB9AF344N MB9AF344LA MB9AF344MA MB9AF344NA MB9AF344LB MB9AF344MB MB9AF344NB MB9AF144L MB9AF144M MB9AF144N MB9AF144LA MB9AF144MA MB9AF144NA MB9AF144LB MB9AF144MB MB9AF144NB MB9AFB42L MB9AFB42M MB9AFB42N MB9AFB42LA MB9AFB42MA MB9AFB42NA MB9AFB42LB MB9AFB42MB MB9AFB42NB MB9AFA42L MB9AFA42M MB9AFA42N MB9AFA42LA MB9AFA42MA MB9AFA42NA MB9AFA42LB MB9AFA42MB MB9AFA42NB MB9AF342L MB9AF342M MB9AF342N MB9AF342LA MB9AF342MA MB9AF342NA MB9AF342LB MB9AF342MB MB9AF342NB MB9AF142L MB9AF142M MB9AF142N MB9AF142LA MB9AF142MA MB9AF142NA MB9AF142LB MB9AF142MB MB9AF142NB MB9AFB41L MB9AFB41M MB9AFB41N MB9AFB41LA MB9AFB41MA MB9AFB41NA MB9AFB41LB MB9AFB41MB MB9AFB41NB MB9AFA41L MB9AFA41M MB9AFA41N MB9AFA41LA MB9AFA41MA MB9AFA41NA MB9AFA41LB MB9AFA41MB MB9AFA41NB MB9AF341L MB9AF341M MB9AF341N MB9AF341LA MB9AF341MA MB9AF341NA MB9AF341LB MB9AF341MB MB9AF341NB MB9AF141L MB9AF141M MB9AF141N MB9AF141LA MB9AF141MA MB9AF141NA MB9AF141LB MB9AF141MB MB9AF141NB FM3_MN706-00024-3v0-E-DE4, January 30, 2015 E R R A T A Page S H E E T Item Description "Table 9 TYPE8 Product list" should be added as indicated by the shading below. Description in this manual TYPE8 Rev. 3.0 viii 512Kbyte 384Kbyte 256Kbyte MB9AF156M MB9AF156N MB9AF156R MB9AF156MA MB9AF156NA MB9AF156RA MB9AF155M MB9AF155N MB9AF155R MB9AF155MA MB9AF155NA MB9AF155RA MB9AF154M MB9AF154N MB9AF154R MB9AF154MA MB9AF154NA MB9AF154RA March 31, 2014 The target products in this manual "Table 8 TYPE7 Product list" should be added as indicated by the shading below. Description in this manual TYPE7 326 Flash memory size CHAPTER 3-1: USB Function 3.3. Operation of each register in response to a command 64Kbyte MB9AFA32L MB9AFA32M MB9AFA32N MB9AF132M MB9AF132N MB9AFAA2L MB9AFAA2M MB9AFAA2N MB9AF1A2L MB9AF1A2M MB9AF1A2N MB9AFA31L MB9AFA31M MB9AFA31N MB9AF131M MB9AF131N MB9AFAA1L MB9AFAA1M MB9AFAA1N MB9AF1A1L MB9AF1A1M MB9AF1A1N "Operation of each register in response to a read command" should be added as below. <Note> When next setup stage is received without "(3) Command end sequence" being carried out due to the process of an interrupt which has higher priority than USB, the device makes no response to the next setup stage. In order to avoid this phenomenon, carry out any of the following. ・Increase the interrupt priority of the Setup stage, Data stage and Command end sequence ・Continue the process of the IN transfer interrupt in the Data stage sequence until DRQO is cleard in the Command end sequence. January 30, 2015, FM3_MN706-00024-3v0-E-DE4 CONFIDENTIAL Flash memory size 128Kbyte 7 E R R A T A Page 629 Item Description APPENDIXES "Table 8 TYPE7 Product list" should be added as indicated by the shading below. D Product TYPE Flash memory size List Description in this manual 128Kbyte 64Kbyte TYPE7 Rev. 4.0 ix 502 MB9AFA32L MB9AFA32M MB9AFA32N MB9AF132M MB9AF132N MB9AFAA2L MB9AFAA2M MB9AFAA2N MB9AF1A2L MB9AF1A2M MB9AF1A2N MB9AFA31L MB9AFA31M MB9AFA31N MB9AF131M MB9AF131N MB9AFAA1L MB9AFAA1M MB9AFAA1N MB9AF1A1L MB9AF1A1M MB9AF1A1N January 30, 2015 The target products in this manual "Table 13 TYPE12 Product list" should be added as indicated by the shading below. Description in this manual TYPE12 502 S H E E T Flash memory size 1.5 Mbytes 1 Mbytes MB9BF529S MB9BF529T MB9BF529SA MB9BF529TA MB9BF429S MB9BF429T MB9BF429SA MB9BF429TA MB9BF329S MB9BF329T MB9BF329SA MB9BF329TA MB9BF129S MB9BF129T MB9BF129SA MB9BF129TA MB9BF528S MB9BF528T MB9BF528SA MB9BF528TA MB9BF428S MB9BF428T MB9BF428SA MB9BF428TA MB9BF328S MB9BF328T MB9BF328SA MB9BF328TA MB9BF128S MB9BF128T MB9BF128SA MB9BF128TA CHAPTER 6-1: "2. Revision" should be added <Attached document 1>. HDMI-CEC/ Remote Control Reception 2. Revision CHAPTER 6-1: "3. Usage notes of HDMI-CEC" should be added <Attached document 2>. HDMI-CEC/ Remote Control Reception 3. Usage notes of HDMI-CEC 8 CONFIDENTIAL FM3_MN706-00024-3v0-E-DE4, January 30, 2015 E R R A T A Page 505 S H E E T Item Description CHAPTER 6-2: Figure of RCCEC_rev3 should be added to "Figure 2-1" as below. CEC Reception/ Clock Division Register Remote Reception Peripheral Count clock Clock Main Clock 2. Configuration clock division counter selector Count clock output (To CEC transmit block) Counter overflow Repeat code detection width setting register Sub clock Start bit detection width setting register Threshold value setting register Minimum pulse width setting register “1” detection Endian conversion Shifter CEC pin Filter Edge detection Comp Rise/fall “0” detection Repeat code detection Start bit detection ACK output ACK mask signal (From CEC transmit block) Line error counter CHAPTER 6-2: CEC Reception/ Remote Reception 3.3.8 ACK detection and interrupt output Error bit output Comp Line error detection Maximum data bit width setting register Minimum data bit width setting register "Table 4-1" should be added as below. Table 4-1 ACK output and ACK interrupt Received ACK ACK destination ADRCE RCADR1, RCADR2 output* interrupt address 0 ACK occur match ACK occur 0x0 to 0xE 0x00 to 0x0E 1 not match NACK not occur 0x0F NACK not occur 0xF NACK occur *: When ACKMEN bit of CEC transmission unit is 1 and during transmission, it will always be NACK. January 30, 2015, FM3_MN706-00024-3v0-E-DE4 CONFIDENTIAL ACK/Error bit output " Fall 517 Data storage register 9 E R R A T A Page 541 Item S H E E T Description CHAPTER 6-3: Figure of RCCEC_rev3 should be added to "Figure 2-1" as below. CEC Transmission APB 2. 2.Block Supplied to each block clock Diagram of CEC Count (about 32kHz) Signal Free Time Transmission Transmission Setting Data Control Transmitting Register Register Register Circuit CEC signal input IBREN • ITSTEN CEC TXEN EOM • START SENDEN ACKMEN To CEC reception block * ACK mask signal Transmission control CEC signal output To interrupt circuit Filter SEND Signal free detection ITST IBR Arbitration detection CHAPTER6-3: CEC Transmission 5.3. Arbitration Lost Detection ACKSV Transmission ACK cycle reception *Pseudo open drain 547 IRQ0 Transmission Status Register "Figure 5-3 Arbitration Lost Detection Period" should be corrected as below. ・RCCEC_rev1 Sampling at about 32kHz cycle “0” output period “1” output period Start of next bit Detection period ・Other than RCCEC_rev1 Sampling at about 32kHz cycle 10 cycle “0” output period “1” output period Start of next bit Detection period 10 CONFIDENTIAL Detection period FM3_MN706-00024-3v0-E-DE4, January 30, 2015 E R R A T A Page 548 S H E E T Item CHAPTER6-3: CEC Transmission 5.4. Signal Free Detection Description Description should be added as below. If 5bit signal free time from last fall edge of previous frame to fall edge of start bit should be secured, set "3" to signal free setting register. RCCEC_rev3 If signal free time should be secured 5bit after other device transmission except this device address, it is available. If SEND bit at the start bit detection interrupt reception is "0", it is possible to determine the transmission from the other device. 564 CHAPTER6-3: The bit6 and bit7 of RCCEC_rev3 should be added to "Transmission control register" as below. CEC bit 7 6 5 4 3 2 1 Transmission Field SENDEN ACKMEN IBREN ITSTEN EOM START Reserved 6.1 Transmission Attribute R/W R/W R/W R/W R/W R/W R/W Control Register 0 0 0 0 0 0 0 Initial value (TXCTRL) 0 TXEN R/W 0 [bit7] SENDEN : Sending flag enable bit This bit controls operation of SEND bit in Transmission status register (TXSTS). bit 0 1 Description Disable SEND bit operation Enable SEND bit operation [bit6] ACKMEN : ACK mask enable bit This bit controls ACK mask. When the ACKMEN bit is "1" and Sending, ACK output is masked. bit 0 1 567 Description Disable ACK mask Enable ACK mask CHAPTER6-3: The bit7 of RCCEC_rev3 should be added to "Transmission status register" as below. CEC bit 7 6 5 4 3 2 Transmission Field SEND IBR ITST Reserved Reserved 6.3 Transmission Attribute R R/W R/W R/W R/W Status Register 0 0 0 0 000 Initial value (TXSTS) 1 0 ACKSV R 0 [bit7] SEND : Sending flag bit This bit indicates that CEC transmission is sending. If SENDEN bit is "1" and CEC transmission is sending from start of start bit to end of ACK bit, this bit is "1". When SENDEN bit is "0", this bit is "0". It is invalid to set this bit. bit 0 1 January 30, 2015, FM3_MN706-00024-3v0-E-DE4 CONFIDENTIAL Description Not sending or SEND bit is "0" Sending (When SENDEN is "1") 11 E R R A T A Page 630 Item S H E E T Description APPENDIXES "Table 13 TYPE12 Product list" should be added as indicated by the shading below. D Product TYPE Flash memory size List Description in this manual 1.5 Mbytes 1 Mbytes 1. Product TYPE List TYPE12 MB9BF529S MB9BF528S MB9BF529T MB9BF528T MB9BF529SA MB9BF528SA MB9BF529TA MB9BF528TA MB9BF429S MB9BF428S MB9BF429T MB9BF428T MB9BF429SA MB9BF428SA MB9BF429TA MB9BF428TA MB9BF329S MB9BF328S MB9BF329T MB9BF328T MB9BF329SA MB9BF328SA MB9BF329TA MB9BF328TA MB9BF129S MB9BF128S MB9BF129T MB9BF128T MB9BF129SA MB9BF128SA MB9BF129TA MB9BF128TA 12 CONFIDENTIAL FM3_MN706-00024-3v0-E-DE4, January 30, 2015 E R R A T A S H E E T <Attached document 1> 2. Revision Revision off HDMI-CEC/remote control reception in each product is as follows. Table 1 List of revision in each product Revision RCCEC_rev1 RCCEC_rev2 MB9AFB44L MB9AFB44M MB9AFB44N MB9AFA44L MB9AFA44M MB9AFA44N MB9AF344L MB9AF344M MB9AF344N MB9AF144L MB9AF144M MB9AF144N MB9AF156M MB9AF156N MB9AF156R MB9AFA32L MB9AFA32M MB9AFA32N MB9AF132M MB9AF132N MB9AFB44LA MB9AFB44MA MB9AFB44NA MB9AFB44LB MB9AFB44MB MB9AFB44NB MB9AFA44LA MB9AFA44MA MB9AFA44NA MB9AFA44LB MB9AFA44MB MB9AFA44NB MB9AF344LA MB9AF344MA MB9AF344NA MB9AF344LB MB9AF344MB MB9AF344NB MB9AF144LA MB9AF144MA MB9AF144NA MB9AF144LB MB9AF144MB MB9AF144NB MB9AF156MA MB9AF156NA MB9AF156RA January 30, 2015, FM3_MN706-00024-3v0-E-DE4 CONFIDENTIAL Product number MB9AFB42L MB9AFB42M MB9AFB42N MB9AFA42L MB9AFA42M MB9AFA42N MB9AF342L MB9AF342M MB9AF342N MB9AF142L MB9AF142M MB9AF142N MB9AF155M MB9AF155N MB9AF155R MB9AFB42LA MB9AFB42MA MB9AFB42NA MB9AFB42LB MB9AFB42MB MB9AFB42NB MB9AFA42LA MB9AFA42MA MB9AFA42NA MB9AFA42LB MB9AFA42MB MB9AFA42NB MB9AF342LA MB9AF342MA MB9AF342NA MB9AF342LB MB9AF342MB MB9AF342NB MB9AF142LA MB9AF142MA MB9AF142NA MB9AF142LB MB9AF142MB MB9AF142NB MB9AF155MA MB9AF155NA MB9AF155RA MB9AFB41L MB9AFB41M MB9AFB41N MB9AFA41L MB9AFA41M MB9AFA41N MB9AF341L MB9AF341M MB9AF341N MB9AF141L MB9AF141M MB9AF141N MB9AF154M MB9AF154N MB9AF154R MB9AFA31L MB9AFA31M MB9AFA31N MB9AF131M MB9AF131N MB9AFB41LA MB9AFB41MA MB9AFB41NA MB9AFB41LB MB9AFB41MB MB9AFB41NB MB9AFA41LA MB9AFA41MA MB9AFA41NA MB9AFA41LB MB9AFA41MB MB9AFA41NB MB9AF341LA MB9AF341MA MB9AF341NA MB9AF341LB MB9AF341MB MB9AF341NB MB9AF141LA MB9AF141MA MB9AF141NA MB9AF141LB MB9AF141MB MB9AF141NB MB9AF154MA MB9AF154NA MB9AF154RA 13 E R R A T A Product number Revision RCCEC_rev2 RCCEC_rev3 14 CONFIDENTIAL S H E E T MB9AFAA2L MB9AFAA2M MB9AFAA2N MB9AF1A2M MB9AF1A2N MB9BF529S MB9BF529T MB9BF429S MB9BF429T MB9BF329S MB9BF329T MB9BF129S MB9BF129T MB9BF529SA MB9BF529TA MB9BF429SA MB9BF429TA MB9BF329SA MB9BF329TA MB9BF129SA MB9BF129TA MB9AFAA1L MB9AFAA1M MB9AFAA1N MB9AF1A1M MB9AF1A1N MB9BF528S MB9BF528T MB9BF428S MB9BF428T MB9BF328S MB9BF328T MB9BF128S MB9BF128T MB9BF528SA MB9BF528TA MB9BF428SA MB9BF428TA MB9BF328SA MB9BF328TA MB9BF128SA MB9BF128TA FM3_MN706-00024-3v0-E-DE4, January 30, 2015 E R R A T A S H E E T <Attached document 2> 3. Usage notes of HDMI-CEC RCCEC_rev1 If external load is large, arbitration lost is occurred. Countermeasure is necessary. (ex. reduce pull-up resistor) Except RCCEC_rev3 If "Polling message" is sent, set "0x0F" to RCADR1 or RCADR2 register for NACK response. If ACK response is done to other device transmission when NACK response is set for "Polling message, set below. 1. Store 0x0 to SFREE register. 2. Monitor CEC line with GPIO and wait until 1 lasts for the signal free time. 3. Store frame data to TXDATA register and store 0x0F to RCADR1 or RCADR2 register. It sends a massage after 3~4 clocks of 32.768kHz clock when TXDATA is stored 0x0F. If the device receives a frame from another node within 2~3 clocks after storing TXDATA, the bus error occurs and if the device receives a frame from another node within 3~4 clocks after storing TXDATA, the arbitration lost occurs. In these cases: 4-A-1. Set RCADR1 or RCADR2 to former value from 0x0F to reply ACK 4-A-2. Return back to step 2 above If the device receives a frame from another node within 1~2 clocks after storing TXDATA, take these steps. 4-A-3. Monitor CEC line with GPIO after 50us from storing TXDATA 4-A-4. Set TXEN to 1-> 0 -> 1 immediately when GPIO finds state low on the CEC line 4-A-5. Set RCADR1 or RCADR2 to former value from 0x0F to reply ACK 4-A-6. Return back to step 2 above Previous frame 2. Signal free time wait 3. TXDATA write January 30, 2015, FM3_MN706-00024-3v0-E-DE4 CONFIDENTIAL 50us 4-B-1. CEC pin check 15 E R R A T A S H E E T If RCADR1 or RCADR2 is changed in middle of communication and bus error occurred, change until rise edge of 8bit. STOP bit 1bit 2bit 7bit 3bit 4bit 8bit 5bit 6bit EOM bit 7bit 8bit EOM bit ACK bit ACK bit Change RCADR1,2 until 8bit of rise edge. When bus error is occurred at 8bit, interrupt is occurred after 35 count clock+2 to 3 PCLK2 from fall edge. 16 CONFIDENTIAL FM3_MN706-00024-3v0-E-DE4, January 30, 2015

© Copyright 2026