Laboratorio 2

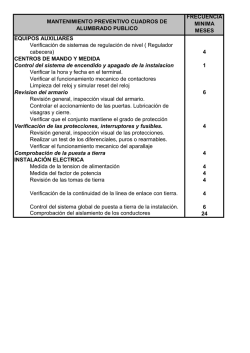

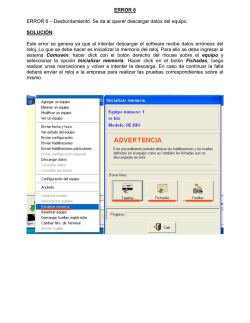

Creación de un Sistema Embebido en Vivado 2° Cuatrimestre 2015 Patricia Borensztejn Laboratorio 2 26/08/2015 IP Integrator • Vamos a utilizar la herramienta IP Integrator de Vivado para conectar dos IP´s de tipo GPIO (General Purpose I/O). Block Design • Nuestro Diseño final será este: Interconexión AXI • La conexión PS-PL se realiza mediante el módulo de interconexión AXI • ¿Qué es AXI? Es una familia de buses introducida por ARM • AXI es un estándar formado por numerosas señales que permiten hacer transferencias entre dispositivos maestros y esclavos. Salvo en el standard stream, la información está mapeada en memoria. AXI • AXI is part of ARM AMBA, a family of micro controller buses first introduced in 1996. The first version of AXI was first included in AMBA 3.0, released in 2003. AMBA 4.0, released in 2010, includes the second version of AXI, AXI4. • There are three types of AXI4 interfaces: – – – AXI4—for high-performance memory-mapped requirements. AXI4-Lite—for simple, low-throughput memory-mapped communication (for example, to and from control and status registers). AXI4-Stream—for high-speed streaming data. • Xilinx introduced these interfaces in the ISE® Design Suite, release 12.3. AXI Interconnect • Dentro del Módulo AXI Interconect hay un núcleo que rutea el tráfico entre las interfaces Esclavas y las Maestras. Otros submódulos internos pueden realizar otras funciones, conversiones de tamaño, de protocolos, colas fifo, etc. Algunos Modelos de Interconexión Modelo buttons AXI GPIO Módulo AXI Interconnect switches Zynq AXI GPIO uart ddr3 Configuración Zynq • Vamos a configurar una de las interfaces M_AXI_GP0 Configuración M_AXI_GP0 • Master quiere decir que es el Zynq el que inicia los pedidos de E/S. Configuración de relojes • Si vamos a usar la interface AXI quiere decir que vamos a usar la parte PL del dispositivo debemos pasarle : – El reloj : PS genera 4 clks para PL: F_CLK_CLK0 • La interconexión AXI necesita: – Un reloj para el crossbar interno: ACLK – Un reloj por cada master o slave: S00_ACLK, M00_ACLK, M01_ACLK • Cada controlador AXI de dispositivo necesita su reloj: s_axi_clk • El propio master de AXI, necesita también su reloj: M_AXI_GP0_ACLK que es la señal de reloj global Relojes Reset (GeneralEnable Clock Resets) • También necesitamos pasar de PS a PL la señal de reset FCLK_RESET0_N. Esta señal es distribuida hacia todos los componentes por un IP: Processor System Reset AXI Interfaces • Aquí vemos las interfaces AXI únicamente, sin externas, ni reloj, ni reset Incluir los IP • Se agregan al diseño seleccionando AXI GPIO • Se les da un nombre: switches • En la parte de configuración se indica la interface: sws 4 bits • Se ejecuta el Run Connection Automation y se selecciona la conexión : de slave a master • Lo mismo para el segundo AXI GPIO, buttons Diseño Completo Mapa de direcciones • Espacio correspondiente a GP0 Conectar las entradas externas • Se puede hacer manualmente pero también automáticamente utilizando Designer Assistance Sintetizar • En la vista synthetisized Design, verificar que I/O planning esta OK y ya mapeados en el constraints. Generar .bit y Exportar • • • • • • El Block Design debe estar abierto Generate Bitstream Open Implemented Design File->Export->Export Hardware Include Bitstream File->Launch SDK SDK • Cerrar antiguos proyectos, dejar únicamente system_wrapper_hw_platform_1 • File->New->Board Support Package – Standalone OS, standalones_bsp_0 • File->New->Application Project – Nombre – Usar existing board support package SDK Creación de librerías • El library generator va a correr y generar el archivo xparameters.h en: • C:\xup\embedded\2014_2_zynq_labs\lab2\la b2.sdk\standalone_bsp_0\ps7_cortexa9_0\inc lude • Copiar este código o bien Importarlo del src Código C • xgpio contiene las funciones • xparameters.h contiene la identificación de los dispositivos Bajar a la placa • Usar un terminal (por ahora no funciona) • Xilinx Tools: Program FPGA • Seleccionar Aplicación y – File->Run as->Launch on Hardware Tarea Labo 2: 1. Hacer que funcione 2. Incorporar los leds: lo que hay en los switches mostrarlo en los leds

© Copyright 2026