Clase 1. 19 de agosto de 2015. Introducción

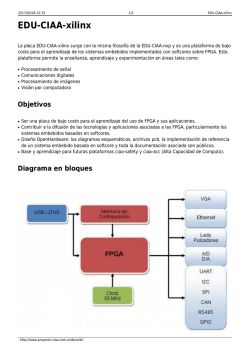

Co-Diseño Hardware Software con FPGA 2° Cuatrimestre 2015 Patricia Borensztejn Introducción 19/08/2015 Resumen • Hace 25 años, uno de los fundadores de la compañía xilinx , Ross Freeman, inventó y patentó el FPGA. Su idea se basó en la Ley de Moore, poner más y más transistores al servicio de la programación y re programación del hardware. • En paralelo, y como consecuencia de la revolución tecnológica también debida al circuito integrado, los sistemas electrónicos embebidos comenzaron a inundar los mercados mundiales, y con ellos comenzó el Co diseño , así llamado pues la interacción entre el hardware y el software comenzaba desde la etapa de descripción funcional del aparato. • En estos 25 años de Co Diseño, los Fpga abrieron un camino nuevo: ya no sólo era posible programar y reprogramar el elemento del software sino también el del hardware. Funciones que inicialmente podían pensarse desde el lado del software, podían pasarse rápidamente al lado del hardware. Y viceversa. Con poco costo de desarrollo. • En este tutorial mostraremos como hacer Co diseño con FPGA utilizando las herramientas de xilinx y algunas ideas metodológicas para aplicar al flujo de diseño. Tres innovaciones desde 1980 • Sistemas Embebidos (década del 70) y SoCs • FPGA (década del 80) • Co-Diseño (década del 90) Sistema Embebido: ¿Que significa? Small device, like a cell phone? Small processor installed in some other device, like a car? Software that controls a consumer device? Must have real-time response? My favorite: Any system where the user doesn’t want to know that it includes a processor Disertación de un consultor de la industria de embebidos, Doug Locke, 2004 Real-Time Embedded Technology and Applications Symposium: Real-Time and Embedded Systems: Past, Present, and Future Sistemas Embebidos: ¿de donde venimos? • El primer sistema embebido se considera: – Sistema de Control del ICBM (Misil Balístico Inter Continental), desarrollado por la Fuerza Aérea de EEUU en 1961. – Formado por transistores y puertas lógicas – Controlaba la trayectoria y estabilidad del misil – (No falla. Siempre la tecnología avanzando a paso redoblado) – Otros consideran que fue AGD Apollo Guidance Computer, pero yo creo que AGD no era un sistema embebido sino una computadora programable. – Durante la primer década, 1970, las aplicaciones de SE eran para defensa y militares. De Wrist Computer a Apple Watch • 1970: Hamilton Pulsar «Wrist Computer», costaba 2100 dólares. Diseñado por George Thiess y Willie Crabtren en Electro-Data, contenía 44 chips. • 1974: Microma y Seiko introducen la tecnología LCD y se integran todas las funciones del LCD y del reloj en un chip, el Intel 5810. Microma LCD Watch • 2014: Apple Watch , ¿qué no tiene? Sistemas Embebidos: El microcontrolador. 1980 • La introducción del microcontrolador, verdadero System on Chip, en la década de los 80, provoca un crecimiento rápido de los sistemas embebidos aplicados a la industria. – 1976 Intel lanza al mercado sus microcontroladores 8048 – En 1985 salen los primeros PIC (pic1650) desarrollados por General Instrument • Los Sistemas Embebidos se construyen alrededor de un microcontrolador. • Las aplicaciones de sistemas embebidos emergen de todas las áreas posibles. Todas. Industrial. Juegos. Mercado de consumo. • Comienza el codiseño 1985 (hace casi 30 años) • Algunas referencias de tiempo: – – – – 1984: IBM AT computer (con el 80286) 1984: Apple introduce Macintosh 1985: IBM anuncia su primera computadora portátil 1985: Microsoft Windows 1.0 • No había: – Explorador de Internet (recién en 1990 se desarrolla el primero ) – Teléfonos celulares (se empiezan a comercializar en los 90) Ross Freeman (1985) • Patente US 4870302: – Configurable electrical circuit having configurable logic elements and configurable interconnects FPGA: 1985 • 1985: primera patente de una FPGA. • Primera Familia: XC2000 – Dos miembros XC2064 y XC2018 – 64 CLB´s (Configurable Logic Block) – 2 LC (Logic Cell) por CLB – LUT de 3 entradas – Max. I/O Pins: 74 – Sistema de Desarrollo : XACT 1.0 FPGA: 1985 Codiseño • Emerge como una disciplina a principios de los 90 • Muy ligada al desarrollo de productos y sistemas embebidos que deben entrar rápidamente en el mercado. • Co-Diseño: proceso de diseño concurrente y coordinado de un sistema electrónico compuesto por elementos de hardware y de software y basado en una descripción del sistema. La implementación de dicho sistema se realiza con la ayuda de herramientas automáticas. • SLD: System Level Design automation Co-Diseño en la Academia • La partición automática de hardware y software se reconoce como una importante área de investigación • 1992: IFIP International Workshop on Hardware/Software Codesign (CODES) • 2003: International Conference on Hardware/Software Codesign and System Synthesis (se une CODES con IEEE Int.Symposium on System Synthesis) IEEE/IFIP/ACM Pero… • Hasta el año 2000, el hardware y el software estaban separados • Hardware: – Circuitos específicos – FPGA • Software corriendo en: – Microcontroladores – Microprocesadores 2001-2002: SoC on FPGA • Introducción del Virtex-II Platform FPGA en marzo 2002 • Concepto de SoC: The Xilinx platform-based FPGA technology brings programmability to the systemon-chip metodology • On chip programmability • On chip hard cores: Power Pc • On chip soft cores: MicroBlaze • Xcelljournal 40 Virtex II: Revoluciona el diseño de sistemas hardware y software • Product of the year award from Electronic Products Magazine. 2001. • The curtains have been raised! The Virtex-II Pro™ Platform FPGA solution – the most sophisticated silicon and software product ever – is now available for programmable system design. Programmable systems represent flexible and scalable systems that are programmable at the architectural level. The goal in developing the Virtex-II Pro FPGA was to revolutionize system architecture by tightly integrating hardware and software functions on a single platform with unprecedented flexibility and scalability. (Xilinx, Anil Telikepali, Xcell, spring 2002) Herramientas de Desarrollo para el Co Diseño • ISE 5.1 incorpora Wind River Systems tools y Celonika DK design suite • Codesign comes to Virtex-II Pro and MicroBlaze Systems. Xcell Journal 44 • En 2003, Xilinx introduce el Embedded Design Suite (EDK): – Microblaze puede ser empleado en dispositivos de la familia Spartan que no incluyen Power Pc como el Virtex II Pro. EDK (2003-2013) • EDK es un entorno integrado de herramientas para el diseño de sistemas embebidos. Incluye los IP necesarios para diseñar FPGAs con PowerPC® (hard processor cores) y/o MicroBlaze™ (soft processor cores). • Está incluído en ISE Design Suite • La última version es ISE 14.7 de octubre 2013 • Pero las cosas siguen cambiando y Xilinx …discontinuó el ISE Design Suite FPGA 2011-2014 • FPGA quiere decir Field Programmable Gate Array. • Pero es obvio que las FPGA ya no son lo que eran. Es decir, son muchísimo mas que un gate array (una tecnología de fabricación de ASICs) programable. • 2011: All Programmable FPGA , All Programmable SoC • All Programmable FPGA es la serie 7: productos de 3 familias: Virtex, Kintex y Artix. No contienen procesadores hard • All Programmable SoC : Zynq-7000 que une un dual core ARM Cortex-A9 core con lógica programable y periféricos en un único dispositivo. • Nuevo entorno de desarrollo : Vivado Design Suite All Programmable SoC: Zynq 7000 • Al revés que en el flujo de diseño de las previas familias de FPGA, es posible configurarlos de forma que lo primero que ocurre es que es el procesador ARM el que bootea cuando se enciende el Zync. Se llama processor centric aproach. • Se programa: – Hardware – Software – Dispositivos de I/O • El flujo de diseño es muy parecido en Vivado que en el EDK • Hay una herramienta nueva que traduce C a HDL Zynq-7000: Product of the Year • 2011: It was named the SoC Product of the year by CMP Media (now called UBM, the publisher of EE Times and EDN), • 2011: It won the IET Innovation Award as well as the Embedded System Product of the Year Award from Elektra (the European Electronics Industry) • 2012:Electronic Products Magazine named the Zynq-7000 its Product of the Year. • 2012:The Microprocessor Report gave the device its Analyst Choice Award. Zynq y Zybo • Zynq es la nueva generación de AllProgrammable System-on-Chip de Xilinx • ZYBO es el nombre de la placa de desarrollo que integra uno de los componentes mas sencillos de la familia Zynq, el Z7010 AP Soc ZYBO y Zynq Zynq-7000: Product of the Year • 2011: It was named the SoC Product of the year by CMP Media (now called UBM, the publisher of EE Times and EDN), • 2011: It won the IET Innovation Award as well as the Embedded System Product of the Year Award from Elektra (the European Electronics Industry) • 2012:Electronic Products Magazine named the Zynq-7000 its Product of the Year. • 2012:The Microprocessor Report gave the device its Analyst Choice Award. Arquitectura Zynq Familia Zync-7000 Familia Zync-7000 ¿En que se diferencia una virtex5 con power pc de una Zynq? (pregunta Bob) The difference is 2 technology generations, (65nm to 28nm), and about 6 years of technical progress. Seriously: read the first data sheet for each family -all the features are listed, one by one. Austin Lesea Principal Engineer Xilinx San Jose Arquitectura de un SoC Arquitectura Zynq Arquitectura Zynq • PS: – Todos los Zynq comparten la misma arquitectura básica construída alrededor del dual ARM CortexA9. Arquitectura Zync • PS: no sólo contiene el ARM, sino también integra otros recursos – APU: Application Processing Unit (APU) – Interfaces con Periféricos de E/S – Interfaces con Memoria – Interconexiones Arquitectura Zync: APU PS: APU • ARM puede operar hasta 1 GHz, dependiendo del dispositivo • L1 separadas en instrucciones y datos de 32KB • L2 compartida por los dos ARM de 512KB • OCP: On Chip Memory de 256KB, accesible por PL y por CPU • ACP: Accelerator coherence port interface para accesos a memoria desde PL a CPU. • SCU: Snoop Control Unit , ademas de mantener coherencia entre las memorias, tiene un rol tambien en la interface entre PS y PL • DMA • Timers • Controlador de Interrupciones PS: APU • Soporte para Programación: SDK de Xilinx • Compilador soporta ARM y Thumb instruction sets (16 y 32 bits) • NEON provee instrucciones SIMD • Unidad FPE: Floating Point Extensions PS: Memory Interfaces • Controladores de memoria dinámica: – Pueden accederse por PL y CPU – 4 ports AXI slaves: uno para ARM, 2 para PL y otro para otro master del sistema • Controladores de memoria estática externa PS: Periféricos I/O • • • • • • • • 2 Ethernet MAC 2 USB 2 CAN 2 SD/SDIO 2 SPI ports 2 UARTS 2 I2C interfaces Todos ellos se comunican con los dispositivos externos mediante un multiplexor MIO a través del cual comparten 54 pines MIO PS: Interconecciones • Todos estos bloques, APU, Interfaces con Memoria, y los IOP se conectan entre si y con PL a través de una conexión AMBA AXI • Esta interconexión es no bloqueante y soporte a la vez varias comunciaciones simultáneas Zynq: Interfaces • Entre PS y PL, y dentro de PS: mediante interconexiones AXI • Entre PS y componentes externos – MIO: Multiplexed Input/Output (54 pines): permite mapear flexiblemente cualquiera de las interfaces standard – EMIO: Extended MIO : no son directas entre PS y conexiones externas, pasa a través de recursos del PL y comparte recursos con éste. Arquitectura Zynq Arquitectura Zync: PL CLB Familia Zync-7000 Input/Output • SelectIO Resources: – Organizados en bancos de 50 IOBs, cada uno de ellos contiene un pad con la conexión física al exterior – Pueden ser • HP (High Performance) : para interfacer con memoria o otros chips con requirimientos de velocidad • o High Range (HR): soporta amplia gama de dispositivos • Otras interfaces (según dispositivos) – GTX Transeivers, bloques IP hard embebidos para altas velocidades Input/Output • Conversores analógicos digitales: XADC • Clocks: el PL recibe 4 señales de reloj del PS, y tiene la capacidad de generar y distribuir su propias señales de reloj independientemente del PS • Programación y Debug: puertos JTAG Interfaces e Interconexiones • Interface: conexión punto a punto para pasar datos, direcciones y señales de control entre master y slaves del sistema • Interconexión: Maneja el tráfico y lo direcciona hacia las interfaces. Interfaces PS-PL • Conjunto de 9 interfaces basadas en AXI, (standard para interfaces de dispositivos y bloques IP) Interfaces PS-PL AXI Dentro del PS, Interfaces AXI se usan para conectar los núcleos ARM con memoria caché, SCU, OCM, y en general con otras interconexiones. Arquitectura Zync Diseño de SoCs con Zynq: Vivado Design Suite VIVADO IDE: Diseño del Hardware VIVADO IDE: IP Integrator Vivado IP Integrator PL: – Creación de IP´s siguiendo el formato standard de la industria IP-XACT – IP´s provenientes de librerias de Xilinx – Métodos (automatizados) para integrar los IP´s al sistema – Uso de HLS (High Level Syntehsis) para crear componentes desde niveles de descripción mas altos VIDADO SDK SDK: Board Support Package • Se elije el SO: ¨light¨, RTOS,Linux, ¨baremetal¨(cuando se comunica directo con el hardware) etc • Incluye device drivers para todos los dispositivos del sistema base (el que se exporta del VIVADO IDE) • Debe refrescarse si se introducen cambios en el Base System (hardware) • La aplicación corre arriba del BSP y SO SDK: herramientas de testing y debugging y profiling • Los diseños que usan tanto PL como PS contienen dos partes: – El archivo .bit que programa la parte PL – El archivo .elf para el PS • Herramientas para co-debugging • Herramientas para debugging del sofware en el hardware Flujo de Diseño 1. 2. 3. 4. Partición harware software Creación del Sistema Base Exportación al SDK y creación BSB y Aplicación Profiling para determinar si la aplicación necesita ser acelerada 5. Uso de la herramienta HLS para crear IP con la parte que deseamos acelerar 6. Volver a crear el Sistema (2) y Aplicación(3) con nuevo IP. 7. Profiling para medir mejora

© Copyright 2026