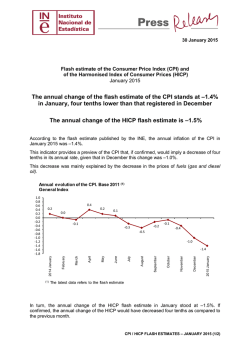

Download - Spansion