Práctica 1

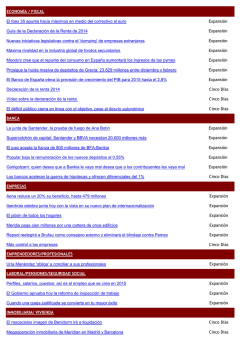

SISTEMAS LÓGICOS COMBINACIONALES Plancha de Problemas: 1) Boole 2) Karnaugh 3) Diseño Combinacional Sistemas Digitales 1 F.C.E.I.A. – U.N.R. 2016 Práctica de manipulación algebraica de funciones booleanas Se pretende que todos los problemas sean resueltos mediante una manipulación algebraica, haciendo uso de las leyes y teoremas del álgebra de Boole. Problema nº 1: Simplificar las siguientes funciones booleanas: a) f1=A’+B’+ABC’ b) f4=ABC+A(B.C)’+A’BC c) f5= A+B’+ABC’ d) f7=A’D’+A’B’+C’D’+BC e) f9=Σ3(1,3,6,7) f) f10=Σ4 (0,1,2,3,6,12,14) Problema nº 2: Determinar las condiciones que deben cumplir las variables booleanas A y B para que se verifiquen las siguientes ecuaciones: a) A’+AB=0 b) AB=AC c) ABD+BCD+A’CD=ABD+A’CD Problema nº 3: Determinar ambas formas canónicas, expresadas tanto algebraica como numéricamente, de las siguientes funciones lógicas: a) f1=A(B’+C’)+C b) f2=AB+AB’C+A’B’ c) f3= ABCD’+ABC’+A’BD d) f4=AB+(A+C)B’+A’B’C e) f5=Σ3 (0,1,3,4,5,7) f) f6=Σ4 (0,1,2,3,12,15) g) f7=(A+B)’ + A’BC+ (A.(B+C))’ h) f8=∏4 (0,3,11,15) i) f9=A’(B+C)(B’+A)+AB’C j) f10=(A’BC+AB’D’)(C+BD)’ Problema nº 4: Demostrar que las siguientes funciones lógicas son EQUIVALENTES: f1= ABC+AB’+AC’+A’BC f2= A+BC Sistemas Digitales 1 Problema nº 5: Dada una función cuya expresión algebraica es: f=(A+B+C)’ ⊕ D’ obtener las expresiones canónicas numéricas de suma de productos y de producto de sumas. Problema nº 6: Demostrar las siguientes propiedades de la función OR-exclusiva: a) A ⊕ B=A’ ⊕ B’=(A’ ⊕ B)’=(A ⊕ B’)’ b) (A ⊕ B)’=AB+A’B’ c) (A ⊕ B)’= A ⊕ B’=A’ ⊕ B d) A(B ⊕ C)=AB ⊕ AC e) A ⊕ 1= A’ f) A ⊕ 0 = A g) Si: A ⊕ C=B ⊕ C , entonces : A=B h) Si: A ⊕ B=0, entonces : A=B i) Si: A ⊕ B ⊕ C=D, entonces: A ⊕ B= C ⊕ D y A= B ⊕ C ⊕ D j) Demostrar si esta identidad es cierta o falsa: A ⊕ (B+C)=(A ⊕ B) + (A ⊕ C) k) A+B= A ⊕ B ⊕ AB l) Usando la ecuación k) cualquier expresión puede ser convertida en otra equivalente conteniendo sólo las operaciones XOR y AND. Transformar la siguiente expresión de esa manera: f=ABC’+AB’C+A’C Problema nº 7: Siendo f= Σ4(5,6,13) y f1=Σ4(0,1,2,3,5,6,8,9,10,11,13) encontrar una función f2 tal que se verifique: f=f1.f2’ Sistemas Digitales 1 Soluciones a los Problemas: Veamos un sumario de las leyes y teoremas del álgebra de Boole que usaremos en la resolución de los problemas: Nro. Orden 1 2 3 4 5 6 7 8 9 11 12 Nombre a) Forma OR b)Forma AND Ley de IDEMPOTENCIA Existencia de ELEMENTOS NEUTROS (Ley de Identidad) Ley de ANULACION (Propiedad de los elementos neutros) Ley CONMUTATIVA Ley ASOCIATIVA A+A=A A.A=A A+0=A A.1=A A+1=1 A.0=0 A+B=B+A (A+B)+C=A+(B+C ) A+A’ =1 A.(B+C)=A.B+AC A+A.B=A A+(A’.B)=A+B (A+B)’=A’.B’ (A’)’=A A.B=B.A (A.B).C=A.(B.C) Ley del INVERSO Ley DISTRIBUTIVA Ley de ABSORCION Ley de MORGAN DOBLE NEGACION (Ley de Involución) A.A’=0 A+B.C=(A+B).(A+C) A.(A+B)=A A.(A’+B)=A.B (A.B)’=A’+B’ En las columnas a) y b) se indican las formas DUALES de representación de cada ley, ya que el PRINCIPIO DE DUALIDAD establece que si en una identidad se intercambian entre sí las operaciones suma y producto lógicos, y los elementos 0 y 1, la identidad permanece válida. De ahora en adelante, para hacer referencia a una determinada identidad la identificaremos por la fila y la columna del cuadro. De esta manera, el indicador(6.a) hará referencia a la identidad A+A’=1. Esto nos permitirá explicar en forma concisa las respectivas leyes usadas en la manipulación algebraica. Solución Problema nro. 1: a) f1=A’+B’+ABC’ 4.b f1=A’+B’+B.AC’ 9.a f1=A’+B’+AC’ 4.a f1= A’+AC’ 9.a + B Sistemas Digitales 1 f1=A’+C’+B’ 4.a f1=A’+B+C’ Aplicando (11.b) podría expresarse: f1=(ABC)’ b) f4=ABC+A(B.C)’ 11.b+A’BC f4=A (BC+(BC)’)+A’BC f4=A+A’BC = A+BC c) f5= A+B’+ABC’ 4.a f5=A+ABC’ 8.a+B’ f5=A+B’ d) f7=A’D’ 2.b+A’B’+C’D’+BC f7=A’D’.1 6.a +A’B’+C’D’ 4.a+BC f7=A’D’(C+C’) 7.a+C’D’+A’B’+BC f7=A’D’C 4.a+A’D’C’ 4.a+C’D’+A’B’+BC f7=A’CD’ 2.b+A’C’D’+C’D’ 7.a+A’B’+BC f7=A’CD’.1 6.a+C’D’(A’+1) 3.aA’B’+BC f7=A’CD’(B+B’) 7.a+C’D’.1 2.b+A’B’+BC f7=A’BCD’+A’B’CD’+C’D’+A’B’+BC 4.a⇒f7=A’BCD’4.b+BC+A’B’CD’+A’B’ 8.a+C’D’ f7=BCA’D’+BC 8.a+A’B’+C’D’ f7=BC+A’B’+C’D’ Sistemas Digitales 1 e) f9=∑3(1,3,6,7) Tener presente que esta forma de notación indica la correpondiente SUMA DE PRODUCTOS CANÓNICOS (minterm). Es decir daría el equivalente decimal de TODAS las filas donde la tabla presenta un “1” a su salida. ABC f9 0 000 0 1 001 1 Para evitar ambigüedades entre la notación NUMÉRICA y la ALGEBRAICA hay que convenir en el ordenamiento que tendrán las variables (literales) en la tabla. Convendemos en asignar el literal que aparezca en primer término entre paréntesis al bit más significativo (MSB) y de ahí en adelante ordenando en forma correlativa. Por ejemplo : 2 010 0 f(X,Z,W)=∑3(1,4)=X’Z’W+XZ’W’ 3 011 1 4 100 0 5 101 0 Se deja constancia que esta CONVENCIÓN no es universal (hay autores que ordenan las tablas al revés). Es simplemente una manera de ponernos de acuerdo en la notación. En caso de no estar especificadas las variables, asignaremos el MSB al literal A, el siguiente al B,etc. Por lo dicho resulta: 6 110 1 7 111 1 Nº F9=∑ 3 (1,3,6,7)=A’B’C+A’BC+ABC’+ABC 001 011 110 111 Notar que cada minterm puede escribirse pensando en la notación binaria del equvalente decimal, sin armar la tabla, negando la variable cuando en la respectiva combinación de entradas el respectivo bit es “0” y dejándola sin negar en caso que sea “1” . f 9= A’C(B’+B) ( 6 a ) +AB(C’+C) (6a) = A’C . 1 (2a) + AB .1 (2a) = A’C+AB f) f 10= ∑ 4 (0,1,2,3,6,12,14) f10= A’B’C’D’+A’B’C’D (7a) +A’B’CD’+A’B’CD(7a) +A’BCD’+ABC’D’+ABCD’(7a) f 10= A’B’C’(D’+D) + A’B’C(D’+D) +A’BCD’+ ABD’(C’+C) f 10= A’B’C’+A’B’C+A’BCD’+ABD’ f 10= A’B’(C’+C) +BD’(A’C+A) (9a) f 10 = A’B’+BD’(C+A) = A’B’+BCD’+ABD’ Observación: notar que la manipulación algebraica no constituye una manera sistemática de simplificación, y no asegura el logro de la máxima simplificación, es decir, la obtención de una expresión MÍNIMA EQUIVALENTE Sistemas Digitales 1 Solución problema Nº 2 a) Para que sean A’+AB (9 a) = A’+B= 0 deben ser A’=0 o sea A=1 y además B=0 Por lo tanto, las condiciones que deben cumplir son: A=1 B=0 b) Para que se verifique AB=AC bien que sea B=C ( A cualquiera) c) ABD+BCD+A’CD= ABD+A’CD ⇒ debe ocurrir que sea A=0 ( ByC cualesquiera) o ⇒ D(AB+BC+A’C) = D(AB+A’C) AB+BC+A’C=AB+A’C Por ley de CONSENSO (10a) la identidad es válida siempre Solución problema Nº 3 a) f1= A(B’+C’)+C dada una expresión algebraica, aplicando la propiedad DISTRIBUTIVA (( 7 a) y (7 b)) primeramente se le lleva a suma de productos o a producto de sumas según cual sea la forma canónica buscada. En el caso de suma de productos, se multiplica cada producto por la suma de las variables que faltan en él y sus inversas ((2b)(6a)), y se distribuye (7a) y se suprimen los términos repetidos (1a) . Es decir : f1= A(B’+C’)+C=AB’+AC’+C f1 = AB’.(C+C’)+AC’.(B+B’)+C.(A+A’).(B+B’) f1 = AB’C+AB’C’+ABC’+AB’C’+.(AC+A’C).(B+B’) f1 = AB’C+AB’C’+ABC’+AB’C’+ABC+AB’C+A’BC+A’B’C f1 = AB’C+AB’C’+ABC’+ABC+A’BC+A’B’C Expresión algebraica de la primer forma canónica tambien llamada SUMA DE PRODUCTOS CANÓNICOS o EXPRESIÓN NORMAL DISJUNTA . La expresión numérica de la primer forma canónica se obtiene reemplazando directamente cada minterm. de la expresión algebraica por su equivalente decimal: Sistemas Digitales 1 f1= ∑ 3 (5,4,6,7,3,1) = ∑ 3 (1,3,4,5,6,7) En el caso de Producto de sumas, se le suma a cada una de las sumas el producto de cada variable que falta en ella por su inversa ((2a) y (6b)), y se distribulle (7 b) y se suprimen los términos repetidos (1 b). Es decir: f1= A.(B’+C’)+C = (A+C).((B’+C’)+C) = A+C = (A+C)+BB’ 7b =1 f1 = (A+C+B).(A+B+C’) = (A+B+C).(A+B’+C) Expresión algebraica de la segunda forma canónica también llamada PRODUCTO DE SUMAS CANÓNICAS o Expresión normal Conjunta. La expresión numérica de la segunda forma canónica se obtiene reemplazando directamente cada maxterm. de la expresión algebraica por su equivalente decimal, teniendo presente en éste caso, para determinarlo, a cada variable negada le corresponde un “1” y a la variable sin negar le corresponde un “0”. Es decir: f1= Π 3 (0,2) Además, podría haberse obtenido la expresión NUMÉRICA DE LA PRIMER FORMA CANÓNICA a partir de la expresión NUMÉRICA DE LA SEGUNDA FORMA CANÓNICA (y viceversa), Nº ABC f reemplazando los símbolos de ∑ y Π (o viceversa), y completando con los números correspondientes a los eventos 0 000 -de entrada no considerados en la expresión de origen para los cuales la función esté ESPECIFICADA. Los eventos de 1 001 1 la entrada para los cuales la función no esté especificada (REDUNDANCIAS), mantienen sus números. Veamos un 2 010 1 ejemplo: 3 011 0 f= ∑ 3 (1,2,5,7)+ ∑ 3 φ (0,4) 4 100 f= Π 3 (3,6). Π 3 φ (0,4) 5 101 1 6 110 0 7 111 1 Si se necesita determinar la expresión numérica de una función partiendo de la expresión NUMERICA de su COMPLEMENTO, bastarí intercambiar los símbolos de ∑ y Π manteniendo los números. Es decir: Sistemas Digitales 1 Si: f = ∑ 3 (1,2,5,7) + ∑ 3 φ (0,4) Si: f = Π 3 (3,6) . Π 3 φ (0,4) ⇒ ⇒ f’ = Π 3 (1,2,5,7) . Π 3 (0,4) f’ = ∑ 3 (3,6) + ∑ 3 φ (0,4) b) f2 = AB+AB’C+A’B’ F2 = ABC+ABC’+AB’C+A’B’(C+C’) f2 = ABC+ABC’+AB’C+A’B’C+A’B’C’ f2 = ∑ 3 (7,6,5,1,0) ⇒ ⇒ ⇒ f2 = Π 3 (2,3,4) f2 = ∑ 3 (0,1,5,6,7) f2 = (A+B’C).(A+B’+C’).(A’´B´C) c) f3 = ABCD’+ABC’+A’BD f3 = ABCD’+ABC’.(D+D’)+A’BD.(C+C’) f3 = ABCD’+ABC’D+ABC’D’+A’BCD+A’BC’D f3 = ∑ 4 (14,13,12,7,5) ⇒ f3 = ∑ 4 (5,7,12,13,14) f3 = Π 3 (0,1,2,3,4,6,8,9,10,11,15) f3=(A+B+C+D).(A+B+C+D’).(A+B+C’+D).(A+B+C’+D’).(A+B’+C+D). (A+B’+C’+D).(A’+B+C+D).(A’+B+C+D’).(A’+B+C’+D).(A’+B+C’+D’). (A’+B’+C’+D’) d) f4 = AB+(A+C)B’+A’B’C f4 = AB+AB’+B’C+A’B’C 8.a = AB+AB’+B’C Sistemas Digitales 1 f4 = (AB+AB’).(C+C’)+B’C.(A+A’) F4 = ABC+ABC’+AB’C+AB’C’+AB’C+A’B’C f4 = ABC+ABC’+AB’C+AB’C’+A’B’C f4 = ∑3 (7,6,5,4,1) ⇒ f4 = Π3 (0,2,3) f4 = (A+B+C).(A+B’+C).(A+B’+C’) Ésta última expresión podría haber sido obtenida expandiendo la expresión algebraica original, de esta manera: f4 = AB+AB’ 7.a y 6.a +B’C = A+B’C f4 = ((A+B’)+CC’).((A+C)+BB’) 7.b = (A+B’).(A+C) distribuyendo: f4 = (A+B’+C).(A+B’+C’).(A+B+C).(A+B’+C) f4 = (A+B’+C).(A+B’+C’).(A+B+C) e) f5 = ∑3 (0,1,3,4,5,7) ⇒ f5 = Π 3 (2,6) f5 = A’B’C’+A’B’C+A’BC+AB’C’+AB’C+ABC f5 = (A+B’+C).(A’+B’+C) f) f6 = ∑ 4 (0,1,2,3,12,15) f6 = A’B’C’D’+A’B’C’D+A’B’CD’+A’B’CD+ABC’D’+ABCD f6 = Π 4 (4,5,6,7,8,9,10,11,13,14) f6=(A+B’+C+D).(A+B’+C+D’).(A+B’+C’+D).(A+B’+C’+D’).(A’+B+C+D).(A’+B+C +D’).(A’+B+C’+D).(A’+B+C’+D’).(A’+B’+C+D’).(A’+B’+C’+D) Sistemas Digitales 1 g) f7 = (A+B)’+A’BC+(A.(B+C))’ f7 = A’B’+A’BC+(A’+(B+C)’) f7 = A’.(B’+BC+1)+B’C’ = A’+B’C’ f7 = A’.(B+B’).(C+C’)+B’C’.(A+A’) f7 = (A’B+A’B’).(C+C’)+AB’C’+A’B’C’ f7 = A’BC+A’BC’+A’B’C+A’B’C’+AB’C’+A’B’C f7 = A’BC+A’BC’+A’B’C+A’B’C’+AB’C’ f7 = ∑ 3 (3,2,1,0,4) = ∑ 3 (0,1,2,3,4) ⇒ F7 = Π 3 (5,6,7) f7 = (A’+B+C’).(A’+B’+C).(A’+B’+C’) Solución problema Nº 4: f1 = ABC+AB’+AC’+A’BC f2 = A+BC Dos funciones lógicas son equivalentes si tienen la misma TABLA DE VERDAD. Dado que la forma canónica extraida de una determinada tabla de verdad es única, si dos funciones tienen la misma expresión CANÓNICA, es que son EQUIVALENTES. Por lo tanto, sacaremos las respectivas formas canónicas de f1 y f2 para ver si son iguales. f1 = ABC+AB’(C+C’)+AC’.(B+B’)+A’BC f1 = ABC+AB’C+AB’C’+ABC’+AB’C’+A’BC f1 = ABC+AB’C+AB’C’+ABC’+A’BC f1 = ∑ 3 (7,5,4,6,3) ⇒ f1 = ∑ 3 (3,,4,5,6,7) f2 = A.(B+B’).(C+C’)+BC.(A+A’) = (AB+AB’).(C+C’)+ABC+A’BC f2 = ABC+ABC’+AB’C+AB’C’+ABC+A’BC Sistemas Digitales 1 f2 = ABC+ABC’+AB’C+AB’C’+A’BC f2 = ∑ 3 (7,6,5,4,3) ⇒ f2 = ∑ 3 (3,4,5,6,7) Por lo tanto, f1 y f2 son EQUIVALENTES. Éste ejemplo permite observar que aunque una forma canónica requiera más símbolos, es más fácil de identificar visualmente por la regularidad de su estructura. Solución problema Nº 5: f1 = A + B + C) ′ donde: f2 = D ′ f1 = A ′B′ C ′ = A ′B′ C ′(D + D ′) = A ′B′ C ′D + A ′B′ C ′D ′ ⇒ f1 = ∑ (1,0) = ∑ (0,1) f = f1 ⊕ f 2 4 4 f2 = D ′ Aparecerán todos los términos cuyo bit menos significativo (LSB) sea cero, es decir, todos los términos pares, por lo tanto: f 2 = ∑ (0,2,4,6,8,10,12,14) 4 Por definición de OR-exclusiva, la función f = f1 ⊕ f 2 adoptará al valor lógico “1” para aquellas combinaciones de entrada para las que las funciones f1 y f2 adopten valores diferentes. Es decir, aparecerán los minterm que aparezcan en una sola de las funciones. Es decir: f = ∑ (1,2,4,6,8,10,12,14) ⇒ f = ∑ (0,3,5,7,9,11,13,15) 4 4 Solución problema Nº 6: Sistemas Digitales 1 a) f1 = A ⊕ B f 2 = A ′ ⊕ B′ f 3 = (A ′ ⊕ B) ′ f 4 = (A ⊕ B′ ) ′ f1 = A ′B + AB′ f 2 = A ′ ⊕ B′ = (A ′) ′B′ + A ′(B′ ) ′ = AB′ + A ′B ⇒ f 2 = f1 f 3 = (A ′ ⊕ B) ′ = ((A ′) ′B + A ′B′ ) ′ = (AB + A ′B′ ) ′ = (AB) ′.(A ′B′ ) ′ = = (A ′ + B′ ).(A + B) = 0 + A ′B + B′ A + 0 ⇒ f 4 = (A ⊕ B′ ) ′ = (A ′B′ + A(B′ ) ′) ′ = (A ′B′ + AB) ′ = f 3 ⇒ b) f1 = (A ⊕ B) ′ f 3 = f1 f 4 = f1 f 2 = AB + A ′B′ f1 = (A ′B + AB′ ) ′ = (A ′B) ′.(AB′ ) ′ = (A + B′ ).(A ′ + B) = 0 + AB + B′ A + 0 = f 2 c) f1 = (A ⊕ B) ′ f 2 = A ⊕ B′ f3 = A ′ ⊕ B f1 = AB + A ′B′ f 2 = A ′B′ + A(B′ ) ′ = A ′B′ + AB ⇒ f 2 = f1 f 3 = (A ′) ′B + A ′B′ = AB + A ′B′ ⇒ f 3 = f1 d) f1 = A(B ⊕ C) f 2 = AB ⊕ AC f1 = A(B ⊕ C) = A(B′ C + BC ′) = AB′ C + ABC ′ f 2 = AB ⊕ AC = (AB) ′(AC) + (AB)(AC) ′ = (A ′ + B′ )AC + AB(A ′ + C ′) f 2 = 0 + AB′ C + 0 + ABC ′ = AB′ C + ABC ′ ∴ f1 = f 2 e) A ⊕ 1 = A ′.1 + A.1′ = A ′ + 1.0 = A ′ f) A ⊕ 0 = A ′.0 + A.0 ′ = 0 + A.1 = A ′ A ⊕ C = A ′C + AC ′ g) A ⊕ C = B ⊕ C ⇒ ⇒ A ′C + AC ′ = B′ C + BC ′ ⇒ A = B B ⊕ C = B′ C + BC ′ A ′B = 0 h) A ⊕ B = 0 ⇒ A ′B + AB′ = 0 ⇒ ⇒A = B AB′ = 0 i) Probaremos primero que si: x ⊕ α = y entonces x = y ⊕ α (1) Si x = α ⇒ y = 0 ⇒ 0 ⊕ α = α = Si x ≠ α ⇒ y = 1 ⇒ 1 ⊕ α = α ′ = x ⇒ queda demostrado (1) x Por lo tanto: Sistemas Digitales 1 A ⊕ (B ⊕ C) = D ⇒ A = (B ⊕ C) ⊕ D (2) (A ⊕ B) ⊕ C = D ⇒ (A ⊕ B) = C ⊕ D (3) Faltaría demostrar: A ⊕ B ⊕ C = A ⊕ (B ⊕ C) = (A ⊕ B) ⊕ C (4) A ⊕ (B ⊕ C) = A ′(B ′ C + BC ′) + A(B ′ C ′ + BC) = A ′B ′ C + A ′BC ′ + AB ′ C ′ + ABC = ∑ (1,2,4,7) 3 (A ⊕ B) ⊕ C = (A ′B ′ + AB)C + (A ′B + AB ′ )C ′ = A ′B ′ C + ABC + A ′BC ′ + AB ′ C ′ = ∑ (1,7,2,4) 3 Además, por definición de XOR, la función adopta el valor “1” cuando hay un número impar de entradas en “1” ⇒ A ⊕ B ⊕ C = ∑ (1,2,4,7) 3 Con lo que queda demostrado (4) 3 (A ⊕ B) ⊕ C = D ⇒ A⊕B = C⊕D A ⊕ B ⊕ C = D ⇒ demostrado 2 A ⊕ (B ⊕ C) = D ⇒ A = (B ⊕ C) ⊕ D = B ⊕ C ⊕ D 4 j) (A ⊕ B) + (A ⊕ C) = A ′B + AB′ + A ′C + AC ′ = A ′(B + C) + A(B ′ + C ′) A ⊕ (B + C) = A ′(B + C) + A(B + C) ′ Por ley de Morgan: (B + C) ′ = B′ C ′ ≠ B′ + C ′ ⇒ (A ⊕ B) + (A ⊕ C) ≠ A ⊕ (B + C) k) f1 = A + B f 2 = A ⊕ B ⊕ AB f 2 = (A ⊕ B) ⊕ AB = (A ′ ⊕ B) ′AB + (A ⊕ B)(AB) ′ = = (A ′B′ + AB)AB + (A ′B + AB′ )(A ′ + B′ ) = = 0 + AB + A ′B + 0 + 0 + AB′ = A(B + B ′ ) + A ′B = A + A ′B = A + B = f1 l) f = ABC ′ + AB A4 B′) = ′ C2+4 ′C = ABC ′ + C(A ′ +2AB 14 4 3 14 4 3′) = ABC ′ + C(A 12 4′ +4 3 7a 9a 12 = ABC ′ + C.[(A B′) ′]′ = ABC ′ + C(AB) ′ = AB ⊕ C 12 4′ +4 3 11a Solución problema Nº 7: f = ∑ (5,6,13) 4 f1 = ∑ (0,1,2,3,5,6,8,9,10,11,13) Sistemas Digitales 1 Como f = f1 .f 2′ , si expresamos las funciones como producto de sumas canónicas (maxterm), los maxterm de f2’ deben completar los maxterm que le falten a f1’ para lograr f, sin agregar ningún maxterm que no esté en f. f = ∏ (0,1,2,3,4,7,8,9,10,11,12,14,15) 4 f1 = ∏ (4,7,12,14,15) 4 Por lo dicho anteriormente será: f 2′ = ∏ (0,1,2,3,8,9,10,11) ∏ ∅(4,7,12,14,15) • 4 14 44424443 puede aparecer o no (seran redundanciasen la tabla de verdad) Aplicando la Doble Negación (12) y la ley de De Morgan (11.b) resulta: f = (f 2′ ) ′ = (∏ (0,1,2,3,8,9,10,11) • ∏ ∅(4,7,12,14,15) Según lo explicado en pág.12, será: f 2 = ∑ (0,1,2,3,8,9,10,11) + ∑ ∅(4,7,12,14,15) 4 4 Notar que los términos redundantes podrían ser incluídos o no, a los efectos de lograr una mayor simplificación en el proceso de minimización de la función. Sistemas Digitales 1 PRÁCTICA de Modelización Algebraica Directa ENUNCIADOS En todos los problemas, escribir de manera directa la/s expresión/es algebraica/s de la/s salida/s. Problema N° 1: La salida Alarma debe activarse (A=1) cuando esté la alarma Habilitada (H=1) y se produce alguna de estas situaciones: Ventana abierta (V=1) o Puerta abierta (P=1). Problema N° 2: Un DEMULTIPLEXOR de 2 canales (C0, C1), una entrada de selección (S) y una entrada de habilitación (H) debe generar una salida (Z), cuyo valor coincida con el valor del respectivo canal de entrada: S=0 Z = C0 S=1 Z = C1 cuando el DEMUX esté habilitado (H=1) o que sea Z=0 cuando el DEMUX esté inhabilitado (H=0). Problema N° 3: Un TANQUE DE AGUA cuenta con 3 sensores de nivel (N1, N2 y N3), una llave selectora (M) y una bomba (B) para su llenado, con los siguientes significados físicos de sus valores lógicos: N1 = 1 nivel por debajo del valor mínimo N2 = 1 nivel igual o por encima del valor intermedio N3 = 1 nivel por debajo del valor máximo M = 1 Modo Manual M = 1 Modo Automático B = 1 bomba encendida A = 1 luz de alarma encendida Escribir de manera directa: a) La expresión algebraica de la función que maneja la bomba de agua (B), de manera que esté encendida si está en Modo Manual y el nivel por debajo del máximo, o si está en Modo Automático y el nivel por debajo del valor intermedio. b) La expresión algebraica de la función que maneja la luz de alarma (A), de manera que esté encendida si el nivel está por debajo del mínimo cuando está en Modo Automático. Problema N° 4: Un SILO DE GRANOS cuenta con sensores de temperatura y de humedad y con una llave selectora de programa, con los siguientes significados físicos de sus valores lógicos: temperatura del silo ≤ admisible T1=1 T2=1 temperatura del silo ≤ temperatura ambiente H1=1 humedad del silo ≥ admisible H2=1 humedad ambiente ≥ 90% P=1 programa manual P=0 programa automático Escribir de manera directa directa, la expresión algebraica de la función que maneja el ventilador (V), si se espera el siguiente comportamiento del mismo: Estará encendido (V=1) si la temperatura del silo es mayor a la admisible o mayor a la temperatura ambiente, en ambos casos, con una humedad ambiente < 90%, o si la humedad del silo es mayor o igual a la admisible en cualquier caso. Todo esto, siempre y cuando esté seleccionado el programa automático. En caso de estar seleccionado el programa manual, debe permanecer encendido permanentemente. SOLUCIONES A LOS PROBLEMAS Problema N° 1: A = H. (V+P) Problema N° 2: Z = (S´.C0+S.C1). H Problema N° 3: a) B = M.N3 + M´.N2´ b) A = N1.M´ Problema N° 4: V = [(T1´+T2´).H2´+H1]. P´+ P Se puede observar que en realidad no es necesario multiplicar el [ ] por P´ ya que si fuese P=1 el otro término forzaría que sea V=1. Esto que puede razonarse intuitivamente, podría haberse deducido aplicando el teorema del Álgebra de Boole: P + P´. X = P + X , quedando: V = (T1´+T2´).H2´+ H1 + P PRÁCTICA de Diseño mediante Interconexión de Bloques Funcionales ENUNCIADOS Diseñar los siguientes circuitos, mediante interconexión de bloques funcionales (en este caso los bloques funcionales serían las compuertas lógicas): Problema 1: Para generar un Código de Paridad, se agrega un Bit de Paridad (Bp) de manera que el nuevo código tenga un nùmero de unos siempre Par (Código de Paridad PAR) o siempre Impar (código de Paridad IMPAR). Estos son Códigos Detectores de Errores de 1 bit, ya que si en el proceso de transmisión un bit llegara cambiado esto afectaría la paridad y el error sería detectado. Se pide diseñar un Generador de Paridad. I3 I2 I1 I0 a) Generador de Paridad PAR b) Generador de Paridad IMPAR Generador de Paridad I3 I2 I1 I0 Bp Problema 2: Se pide diseñar un Comparador de Palabras de 2 bits (A = A1A0, B = B1B0). A1 A0 B1 B0 Si A>B Si B>A Si A=B Comparador de Palabras MA MB I MA=1 MB=1 I=1 Problema 3: Se pide diseñar un Detector de Paridad. Al recibirse el código (4 bits de Información y 1 bit de Paridad), se genera una salida P=1 si la paridad es la esperada. I3 I2 I1 I0 Detector de Paridad a) PAR: P=1 si la Paridad es PAR b) IMPAR: P=1 si la Paridad es IMPAR Generador de Paridad P Problema 4: Diseñar un Inversor Controlado de 4 bits: E3 E2 E1 E0 C Inversor Controlado S3 S2 S1 Si C=1 Sn=E´ (invierte) Si C=0 Sn=E (no invierte) S0 Problema 5: Como ejemplo típico de Diseño mediante Bloques Funcionales podemos nombrar a los circuitos aritméticos. Supongamos que se pretende diseñar un Sumador Total (Full Adder) capaz de sumar los 2 bits correspondientes a la posición “n” de los números A y B y el acarreo de la etapa anterior. an cn+1 bn FULL ADDER sn Resolverlo por interconexión de compuertas lógicas. cn PRÁCTICA de Diseño Tabular (mediante Tablas de Verdad) ENUNCIADOS En todos los problemas se pide hacer el diagrama de E/S con diccionario, la Tabla de Verdad, los mapas de Karnaugh y las ecuaciones mínimas e implementar circuitalmente con compuertas lógicas. Problema 1: Diseñar un Circuito de Mayoría, con 3 entradas y 1 salida, la cual debe ponerse en alto cuando haya mayoría de “1´s” a su entrada. Problema 2: Diseñar un conversor de código Binario de 4 bits a código Gray. B3 B2 B1 B0 Binario / Gray G3 G2 G1 G0 Problema 3: Diseñar un conversor de código BCD (decimal codificado en binario) a 7 segmentos, para excitar un display. B3 B2 B1 B0 a f g b e d c BCD / 7 seg a b c Problema 4: Diseñar un conversor de código Binario de 4 bits a código BCD. A3 B3 B2 B1 B0 A2 A1 A0 C3 C2 C1 C0 d e f g Problema 5: Diseñar un conversor de código Gray de 4 bits a código Binario. G3 G2 G1 G0 Gray / Binario B3 B2 B1 B0 Problema 6: Diseñar un dispositivo integrado por 4 teclas y 2 lámparas indicadoras, al cual llega la señal de un Reloj (R), de manera que: T3 T2 T1 T0 La lámpara intermitente (LI) se enciende y apaga a la frecuencia del reloj cuando: R t • No se pulsa ninguna tecla • Se pulsa sólo una tecla • Se pulsan sólo T2 y T0 La lámpara fija (LF) se enciende cuando no se cumple ninguna LI LF de las condiciones anteriores. Problema 7: Diseñar un Multiplicador binario de dos números de 2 bits: A1 A0 B1 B0 Multiplicador C3 C2 C1 C0 Problema 8: Para controlar el llenado de un tanque de agua se dispone de 2 sensores ubicados a distintos niveles (N1 inferior, N2 superior). Éstos presentan un nivel lógico “1” a su salida cuando les toca el agua. Para el llenado del tanque se dispone de 2 bombas A y B, y hay una válvula de consumo cuya posición también es sensada (V=1 válvula abierta). El llenado del tanque debe hacerse de la siguiente manera: • Si el nivel del agua está por debajo de los dos sensores, deben funcionar ambas bombas. • Si el nivel del agua está entre sensores y la válvula está abierta, deben funcionar ambas bombas. • Si el nivel del agua está entre sensores y la válvula está cerrada, sólo debe funcionar la bomba A. • Si el nivel llega al sensor superior (tanque lleno), deben estar ambas bombas apagadas. Problema 9: A un sistema ingresa un código de 4 bits que nunca puede contener más de 3 bits en “1”. El sistema debe encender una lámpara L1 cuando el número de variables de entrada en “1” sea superior al número de variables de entrada en “0” y encender una lámpara L2 cuando sean iguales. C3 L2 C2 C1 C0 L1 Problema 10: Un codificador de posición de eje proporciona una señal de 4 bits que indica la posición de un eje en pasos de 30º usando un código reflejado (Gray), como se indica en la tabla siguiente. Se puede suponer que las 4 combinaciones posibles de 4 bits no usados, no se producirán jamás. Se desea diseñar un sistema que dadas estas señales, genere una señal S que sea “1” siempre que el eje se encuentre dentro del primer cuadrante (0º - 89º) Al resolver el problema, respetar la definición de Tabla de Verdad en cuanto a la manera de estructurarla. Posición del eje 0º - 29º 30º - 59º 60º - 89º 90º - 119º 120º - 149º 150º - 179º 180º - 209º 210º - 239º 240º - 269º 270º - 299º 300º - 329º 330º - 359º E1 0 0 0 0 0 0 1 1 1 1 1 1 Salida del Codificador E2 E3 0 1 0 1 1 1 1 1 1 0 1 0 1 0 1 0 1 1 1 1 0 1 0 1 E4 1 0 0 1 1 0 0 1 1 0 0 1 Práctica de Implementación de Funciones lógicas con circuitos MSI Implementar la siguiente función lógica: F(A,B,C)=∑mi(3,5,6,7) mediante Multiplexor y Decodificador. 3 Implementación con MUX “1” 7 6 5 4 3 2 1 0 F Z MUX 2 1 0 “0” A B C AB C 0 1 00 0 0 01 0 1 11 1 1 10 0 1 Si se conectan las variables de entrada (A,B,C) a las entradas de Selección (S1S2) del Mux y “1” a los Canales 3,5,6,7 y “0” a los Canales 0,1,2,4, a la salida tendremos la función F, ya que las variables seleccionan el canal por donde viene el respectivo valor de la salida. Siempre Se puede implementar una función de N variables con un Mux de 2N canales. En realidad también se puede implementar con un Mux de 2N-1 canales ingresando una de las variables por los canales de entrada. En caso de necesitar hacerlo, elegir para “fusionar” una de las que aparezca sin negar a la entrada, de manera de no necesitar una NOT. “1” C “0” 3 2 1 0 F MUX 1 0 A B Implementación con DECOD A 7 6 B C 2 1 0 DECODIF 5 4 3 2 A 1 0 7 B C 2 1 0 DECODIF 6 5 4 3 2 1 0 Para implementar la función basta con conectar una OR a los respectivos minitérminos (en caso que las salidas del DECOD fuesen normales) o una NAND (en caso que las salidas del DECOD estuviesen negadas). Esto es así porque por De Morgan: (A´. B´)´= A´´+B´´ = A+B

© Copyright 2026