Tecnología de Dispositivos y Componentes

Universidad de Sevilla

Escuela Superior de Ingenieros

DEPARTAMENTO DE

INGENIERÍA ELECTRÓNICA

Tecnología de Dispositivos y Componentes

Dispositivos electrónicos

Francisco Colodro Ruiz

Juan García Ortega

Carlos Janer Jiménez

2

Tabla de contenidos:

CAPÍTULO 1 ...................................................................................................................... 5

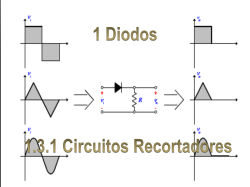

EL DIODO .......................................................................................................................... 5

1.1

EL DIODO DE UNIÓN PN. .......................................................................................... 5

1.1.1 El diodo rectificador ......................................................................................... 8

1.1.2 El diodo Zener ................................................................................................... 9

1.2

EL DIODO SCHOTTKY ............................................................................................... 9

1.3

MODELO DE GRAN SEÑAL DEL DIODO..................................................................... 11

1.3.1 Análisis gráfico de circuitos con diodos ......................................................... 12

1.3.2 Modelos aproximados del diodo ..................................................................... 14

1.3.3 Análisis en continua de circuitos con diodos .................................................. 19

1.4

CIRCUITOS RECTIFICADORES .................................................................................. 21

1.4.1 Fundamentos de la rectificación ..................................................................... 21

1.4.2 Circuito rectificador de media onda ............................................................... 23

1.4.3 Circuito rectificador de onda completa .......................................................... 26

1.5

CIRCUITOS RECTIFICADORES CON CONDENSADOR.................................................. 28

1.6

CIRCUITO REGULADOR CON DIODO ZENER ............................................................ 32

1.7

DETECTOR DE ENVOLVENTE .................................................................................. 35

1.8

EJERCICIOS RESUELTOS .......................................................................................... 43

1.9

EJERCICIOS PROPUESTOS ........................................................................................ 47

CAPÍTULO 2 .................................................................................................................... 52

EL TRANSISTOR BIPOLAR BJT ................................................................................ 52

2.1

ESTRUCTURA DEL TRANSISTOR BIPOLAR DE UNIÓN (BJT). ...................................... 52

2.2

DIAGRAMA DE CORRIENTES EN UN BJT ................................................................. 53

2.3

GANANCIAS DE CORRIENTE CONTINUA DEL TRANSISTOR ....................................... 56

2.4

MODELOS ESTÁTICOS Y GRAN SEÑAL DEL BJT ...................................................... 59

2.4.1 Modelo de gran señal (Ebers-Moll) ................................................................ 59

2.4.2 Modelo simplificado ........................................................................................ 62

3

2.5

CARACTERÍSTICA ESTÁTICA EN EMISOR COMÚN .................................................... 64

2.6

EL TRANSISTOR SCHOTTKY .................................................................................... 68

2.7

EJERCICIOS PROPUESTOS ........................................................................................ 69

CAPÍTULO 3 .................................................................................................................... 74

DISPOSITIVOS FOTÓNICOS ....................................................................................... 74

3.1

EL DIODO EMISOR DE LUZ (LED) ........................................................................... 75

3.1.1 Mecanismos de recombinación de portadores................................................ 76

3.1.2 Característica de los dispositivos semiconductores emisores de luz .............. 77

3.2

DISPOSITIVOS FOTODETECTORES. .......................................................................... 78

3.2.1 Fotoconductores.............................................................................................. 80

3.2.2 El Fotodiodo PIN ........................................................................................... 81

3.2.3 El fotodiodo de Avalancha (APD) .................................................................. 84

3.2.4 El fototransistor .............................................................................................. 84

3.3

LA FIBRA ÓPTICA .................................................................................................. 85

CAPÍTULO 4 .................................................................................................................... 87

EL TRANSISTOR JFET ................................................................................................. 87

4.1

INTRODUCCIÓN. ..................................................................................................... 87

4.2

CARACTERÍSTICA ESTÁTICA ................................................................................... 88

4.2.1 Principios de funcionamiento ......................................................................... 88

4.2.2 Símbolos eléctricos ......................................................................................... 93

4.2.3 Ecuaciones características ............................................................................. 94

4.3

COMPARACIÓN ENTRE PARÁMETROS DEL JFET Y DEL BJT ....................................... 95

CAPÍTULO 5 .................................................................................................................... 96

EL TRANSISTOR MOSFET .......................................................................................... 96

5.1

INTRODUCCION ...................................................................................................... 96

5.2

LA ESTRUCTURA MOS ........................................................................................... 98

5.2.1 La estructura MOS en equilibrio térmico ....................................................... 99

5.2.2 Tensión de banda plana ................................................................................ 102

4

5.2.3 Región de acumulación y deserción.............................................................. 105

Acumulación ............................................................................................................. 105

Deserción .................................................................................................................. 106

5.2.4 Región de inversión ....................................................................................... 108

5.3

LA ESTRUCTURA DE TRES TERMINALES ................................................................ 114

5.4

EL TRANSISTOR MOS .......................................................................................... 117

5.4.1 Obtención de la característica I-V ................................................................ 119

5.5

REGIONES DE FUNCIONAMIENTO .......................................................................... 122

5.5.1 Modulación de la longitud del canal ............................................................ 123

5.5.2 Características I-V. Transistores de empobrecimiento ................................ 124

5.6

SÍMBOLOS ELÉCTRICOS ........................................................................................ 127

5.7

EJERCICIOS PROPUESTOS ...................................................................................... 129

CAPÍTULO 6 .................................................................................................................. 133

MODELOS DE PEQUEÑA SEÑAL ............................................................................ 133

6.1

MODELO DE PEQUEÑA SEÑAL DEL TRANSISTOR BIPOLAR ..................................... 135

6.1.1 Modelo en .................................................................................................. 135

6.1.2 Modelo híbrido o de parámetros h ............................................................... 139

6.1.3 Cálculo de los parámetros de pequeña señal ............................................... 140

6.2

MODELO DE PEQUEÑA SEÑAL DEL JFET .............................................................. 142

6.3

MODELO DE PEQUEÑA SEÑAL ............................................................................... 143

6.3.1 Modelo de baja frecuencia ............................................................................ 143

6.3.2 Modelo de alta frecuencia............................................................................. 145

6.4

EJERCICIOS PROPUESTOS ...................................................................................... 149

5

CAPÍTULO 1

EL DIODO

Los diodos son dispositivos de dos terminales en cuya estructura existe una única unión

entre dos materiales diferentes. La unión más común es la formada por un semiconductor p y otro

n, pero no es la única. Uniones metal-semiconductor y otras más complejas, como la unión PIN

también son utilizadas para fabricar este dispositivo.

1.1

EL DIODO DE UNIÓN PN.

Un diodo de unión pn es el resultado de unir un semiconductor p y otro n, añadirle dos

terminales (cátodo y ánodo) y finalmente encapsularlo. En la Figura 1 se muestra la estructura

anterior así como las referencias de tensión (vd) y corriente utilizadas (id).

VD

ID

P

N

Ánodo

Cátodo

Encapsulado

Figura 1: Estructura de un diodo de unión pn

La relación existente entre la tensión aplicada al diodo y la corriente que circula por él es

la correspondiente a la de una unión pn, se denomina característica estática [id = id(vd)] y se

muestra en la Figura 2.

6

ID

(mA) 18

Región de

polarización

directa

16

IF

10

8

P=VF·IF

6

4

(V)

80

70

VBR

2

50

40

30

20

10

Región de

polarización

inversa

0,5

IR

0,7

VT

(V)

VF

VD

1

2

3 (µA)

Región de

ruptura

Figura 2: Característica estática del diodo.

En el funcionamiento del diodo se distinguen tres regiones bien diferenciadas;

polarización directa, polarización inversa y ruptura. Las dos primeras responden a una relación

exponencial entre id y vd, y le dan el carácter rectificador al diodo, entendido éste como la

capacidad de permitir el paso de corriente positiva pero no de corriente negativa. La región de

ruptura es causada por el efector túnel y por fenómenos de avalancha de portadores, e implica la

ruptura del mecanismo de resistencia al paso de corriente negativa por el diodo.

En la curva anterior se definen varios parámetros característicos:

-

Si se incrementa la tensión del diodo vd partiendo de cero, observaremos como la

corriente id que lo atraviesa es muy pequeña, casi nula, para las primeras décimas de

voltios. Debido al carácter exponencial de la curva, llegará un momento en el cual se

observará cómo la corriente empieza a aumentar de forma considerable. La tensión a la

que comienza a observar corriente se denomina tensión umbral (VT) (por su inicial en

inglés, threshold).

7

-

Los diodos están diseñados para trabajar en unas condiciones de funcionamiento

típicas. Así, la tensión y corriente en directa para las cuales están diseñadas un diodo

se denotan por VF e IF (por su inicial en inglés, forward). En la práctica las tensiones

umbral y directa suelen tomarse iguales. Para un diodo de germanio la tensión en

directa se encuentra alrededor de 0,3 V mientras que para uno de silicio asciende hasta

los 0,7 V.

-

Si desde cero vamos aplicando una tensión vd negativa se observará que la corriente id

que atraviesa el diodo es negativa, pequeña (casi nula) y prácticamente independiente

de la tensión aplicada. Esta corriente aumenta con la temperatura y se denomina

corriente de fuga o inversa (Ir) (por su inicial en inglés, reverse).

-

La corriente inversa continúa siendo prácticamente constante hasta alcanzar la tensión

Zener o de ruptura (VBR) (por su inicial en inglés, breakdown). A partir de ese

instante el valor de la corriente comienza a aumentar bruscamente, permaneciendo la

tensión del diodo aproximadamente constante.

-

La potencia instantánea que disipa un diodo es P(t) = vd · id, siendo vd e id la tensión

aplicada al diodo y la corriente que lo atraviesa en ese instante. La máxima disipación

potencia representa en máximo valor que puede alcanzar el producto tensión por

corriente antes de que el diodo pueda ser dañado por el calor. La potencia máxima

(Pmax) se define para una cierta temperatura ambiente y puede variar si esta

temperatura cambia. Dado que las tensiones en directa (VF) y ruptura (VBR)

permanecen casi constante, la limitación en potencia supone una limitación en la

corriente máxima que puede atravesar el diodo.

Estos parámetros, y otros como los valores de capacidades, tiempo de recuperación

inversa y rango de temperatura de operación, aparecen en las hojas de catálogo (datasheet) de los

fabricantes, y sirven para seleccionar el dispositivo más adecuado para la aplicación que se esté

considerando.

Existen varios tipos de diodos, cada uno de ellos con unas características eléctricas

adecuadas para uno o varios tipos de aplicación concreta.

8

1.1.1 El diodo rectificador

Un diodo rectificador está diseñado para ser utilizado en las regiones de polarización

directa (conducción) e inversa (corte), pero no en la zona de ruptura. En la Figura 3 se muestra el

símbolo eléctrico de este tipo de diodo, así como las referencias de tensión y corriente utilizadas.

VD

ID

ánodo

cátodo

Figura 3: Símbolo eléctrico del diodo rectificador.

Los diodos rectificadores tienen una tensión de ruptura muy alta. Debido a esto, cualquier

corriente negativa de valor apreciable que pueda circular por él provocaría una disipación de

potencia muy elevada. En definitiva, los diodos rectificadores corren el riesgo de destruirse en

cuanto se internan en la zona de ruptura, por lo que en la práctica se considera que ésta es una

región de funcionamiento prohibido.

Los diodos rectificadores suelen ser de silicio, o germanio y entre sus características de

catálogo están:

Tensión directa (VF) del orden de 0,7 V para los de silicio y 0,3 V para los de germanio.

Corrientes inversas (Ir). El rango de variación de estas corrientes van desde los nA para

temperaturas de la unión de pocos grados centígrados hasta uA para los 200º C. Para diodos

de características similares, los de germanio tienen una corriente inversa mayor que los de

silicio.

Tensiones de rupturas (VBR) superiores para los de silicio (1000 V) que para los de

germanio (400 V).

Temperaturas máximas de funcionamiento (Tmax). Los diodos de silicio pueden usarse en

aplicaciones en las cuales se alcancen temperaturas de 200º C mientras que los de germanio

no llegan a 100º C.

9

Aunque la menor tensión directa del germanio frente al silicio pueda significar una

ventaja, las mayores corrientes inversas y las relativamente bajas tensiones de ruptura hacen de los

diodos de silicio los más utilizados para aplicaciones tales como las de rectificación de ondas,

donde los diodos alternan continuamente entre las regiones de conducción y corte.

1.1.2 El diodo Zener

A diferencia del diodo rectificador, el diodo Zener está diseñado para trabajar en las tres

zonas de funcionamiento de la característica estática. En particular, suele incluirse como limitador

de tensión en diferentes aplicaciones electrónicas, como reguladores de tensión, mientras éste

funciona en la zona de ruptura.

La estructura de un diodo Zener contiene una unión pn fuertemente dopada, lo que hace

que los portadores puedan atravesar la zona de carga espacial por efecto Tunel. Controlando la

intensidad del dopado se consigue variar la tensión de ruptura dentro de un rango de 1,2 y 200

voltios.

VD

ID

ánodo

cátodo

Figura 4: Símbolo eléctrico del diodo Zener.

1.2

EL DIODO SCHOTTKY

Un diodo Schottky es un dispositivo electrónico formado por una unión rectificadora

metal-semiconductor. El metal se deposita generalmente en un tipo de material N, debido a la

movilidad más grande de los portadores en este tipo de material (Figura 5).

10

VD

ID

M

N

Ánodo

Cátodo

Encapsulado

Figura 5: Estructura de un diodo Schottky.

Entre las características eléctricas del diodo Shottky están:

Tensión umbral baja. Del orden de 0,2 V.

Tiempos de conmutación bajos. Debido a que las corrientes están formadas prácticamente

por portadores mayoritarios, no existirán tiempos de almacenamiento ni capacidades de

difusión. Si existirán capacidades de transición. El tiempo de conmutación puede llegar a

ser menor de 1 ns.

Corrientes inversas mayores que la de la unión pn.

Tensiones de rupturas menores que las de la unión pn.

El símbolo de un diodo Schottky se muestra en la Figura 6. Debido a su baja tensión de

ruptura y alta corriente en inversa, este diodo no es utilizado en funciones rectificadoras. La

principal ventaja es su tiempo de conmutación, que lo hace ideal para aplicaciones de alta

frecuencia.

VD

ID

ánodo

cátodo

Figura 6: Símbolo eléctrico del diodo Schottky.

11

1.3

MODELO DE GRAN SEÑAL DEL DIODO

En apartados anteriores se ha estudiado uno de los dispositivos electrónicos de estado

sólido más sencillo de construir. Tal y como se vio, el diodo está construido con una única unión

pn. Del estudio de los principios físicos de funcionamiento se llegó a establecer la característica

estática Tensión-Corriente, cuya expresión matemática permite relacionar la tensión entre ánodo y

cátodo (VD) y la corriente (ID) que fluye desde el ánodo al cátodo:

Ecuación 1

I D I o (eVD / VT 1); VT k T / q

donde Io es la corriente inversa de saturación y VT el potencial equivalente de temperatura.

Una de las desventajas que tiene dicho modelo desde el punto de vista de la analítica es la

relación exponencial. Siempre que los elementos que componen un circuito sean lineales

(resistencia, condensador, bobina, fuentes de tensión y corrientes independientes,...), éste puede ser

analizado utilizando alguna o varias de las técnicas analíticas y numéricas que se han desarrollado

para el análisis de sistemas y circuitos lineales. Sin embargo, si el circuito tiene algunos de los

dispositivos electrónicos que se estudian en este curso, en la mayoría de los casos no se encuentran

soluciones analíticas y las técnicas numéricas requieren un alto coste computacional 1. Para ilustrar

este párrafo procedamos con un ejemplo.

Figura 7: Circuito rectificador de media onda.

1

Tiempo empleado por un ordenador en resolver un problema.

12

Supongamos conocida (bien porque la suministra el fabricante en las hojas de

características del dispositivo o bien porque se mide en laboratorio) la corriente inversa de

saturación del diodo de la Figura 7. Aplicando la ley de Kirchhoff de las tensiones al circuito, la

ecuación que tenemos que resolver para conocer VD es

Ecuación 2

VS R I o (eVD / VT 1) VD

La Ecuación 2 no admite solución analítica y es necesario recurrir a técnicas numéricas, en

la mayoría de los casos asistidas por ordenador. En este último caso, el ordenador tendrá que

evaluar varias veces la función exponencial2 siguiendo un determinado algoritmo hasta encontrar la

solución. El problema aún se agrava más cuando el circuito que queremos analizar está constituido

por decenas o incluso centenas de dispositivos no lineales. En tal caso el tiempo requerido para el

análisis puede ser tan grande que el diseño del circuito resulta una tarea impracticable.

En este apartado presentaremos algunos modelos del diodo que permitan la obtención de

soluciones analíticas de circuitos sencillos con diodos. Estos modelos se caracterizan porque las

fuentes de tensión que alimentan los circuitos, o las señales que son procesadas por los mismos,

toman valores relativamente altos cuando se comparan con los valores típicos de tensiones

umbrales de los diodos (0.6V para el silicio y 0.35V para el germanio). Por ello reciben el nombre

de modelos de gran señal. Los modelos aproximarán la curva característica del diodo, dada por la

Ecuación 1, por una curva poligonal (construida por tramos rectos). De esta manera, en

determinadas regiones de funcionamiento del diodo, éste se aproximará por un circuito lineal

constituido por la combinación de fuentes de tensión independientes y resistencias, facilitando el

análisis.

1.3.1 Análisis gráfico de circuitos con diodos

El circuito de la Figura 7 puede también ser resuelto mediante la aplicación de técnicas

gráficas. Si bien estas técnicas son bastante intuitivas, su aplicación se restringe a casos muy

2

Esta es una operación con mayor coste computacional que la suma y el producto, operaciones a las que se reduce el

análisis de un circuito lineal

13

sencillos donde, de manera inmediata, suministran ideas cualitativas del funcionamiento del

circuito, amén de algunos resultados numéricos.

La Ecuación 2 que permite obtener el valor de VD puede formularse como

Ecuación 3

VS I D R V D I D

V D VS

R

R

Por tanto, por la aplicación de las leyes de Kirchhoff, además de la relación exponencial

de la curva ID -VD dada por la Ecuación 2, existe una relación lineal3 ID -VD, dada por la Ecuación 3.

Si ahora representamos gráficamente ambas expresiones sobre el mismo plano ID -VD, como la

corriente y la tensión del diodo deben verificar ambas ecuaciones, la solución que buscamos será

necesariamente la intersección de la curva exponencial y la recta. Este método está ilustrado en la

Figura 8.

Figura 8. Solución gráfica del circuito rectificador.

3

Esta relación es conocida en el argot electrónico como recta de carga. El nombre se justificará cuando se estudie el

transistor bipolar

14

1.3.2 Modelos aproximados del diodo

En la Figura 9.(a) se representa de nuevo la característica Tensión-Corriente del diodo

junto con su símbolo. La corriente es prácticamente nula para tensiones pequeñas y negativas. Sin

embargo, debido al carácter exponencial de la relación V-I, la corriente crece drásticamente cuando

la tensión se aproxima a un valor de tensión VT. Cuando el dispositivo está polarizado en directa

(estado ON) la corriente no puede ser tan grande como se quiera4, si a esto unimos que pequeñas

variaciones de tensión provocan bruscas variaciones de corriente, en polarización directa la tensión

real del diodo será aproximadamente VT. Por todo ello, en la práctica se utilizan con profusión el

modelo representado en la Figura 9.(c).

Figura 9. Diferentes modelos eléctricos del diodo.

Según este modelo, cuando la tensión VD es menor que VT el diodo estará polarizado en

inversa (estado OFF) y a través de él no circulará corriente (se comporta como un circuito abierto).

No obstante, cuando esté polarizado en directa, VD estará fijada a una tensión igual a VT

independientemente de la corriente que fluya entre sus terminales (se comporta como una fuente

constante de tensión). Matemáticamente:

15

Ecuación 4. Modelo simplificado del diodo.

ID 0

VD VT

si VD VT

si I D 0

En la mayoría de los diodos reales la tensión umbral es sólo unas décimas de voltio,

pudiéndose simplificar aún más el modelo de la Figura 9.(c), igualando VT a cero, como se

representa en la Figura 9.(b). En este último caso, cuando el dispositivo esté polarizado en directa

se comportará como un cortocircuito. Un modelo más exacto se representa en la Figura 9.(d) donde

se ha incluido una pequeña resistencia Ron en serie con la fuente VT. Esta resistencia modela la

desviación de la curva exponencial respecto de una línea recta vertical. Ron es un efecto asociado a

la propia unión pn, es decir, existiría independientemente de que hubiera o no caída de tensión en

las regiones neutras del diodo y su valor es la inversa de la pendiente de la recta de la Figura 9.(d).

Como ya se sabe, la hipótesis de que toda la tensión aplicada externamente entre los

terminales del diodo recae en la región de carga espacial no es cierta en dispositivos reales. Las

regiones neutras están fabricadas con un material (semiconductor tipo p o n) con una conductividad

muy alta pero finita, ofreciendo alguna resistencia a la circulación de corriente. También ofrecen

alguna resistencia al paso de la corriente los contactos óhmicos. Este efecto puede ser modelado

incluyendo una resistencia serie RS, la cual suele tomar un valor entorno al ohmio, produciendo

caídas de tensiones despreciables para valores bajos y moderados de corriente. Sin embargo, para

los valores altos de corriente, típicos en dispositivos de potencia, a la caída de tensión VT hay que

sumarle la caída de tensión en RS, perdiendo la relación ID-VD el carácter exponencial. Este efecto

se ilustra en la Figura 10. Ahora, la tensión VD vista externamente en el diodo es la suma de VT

(región de carga espacial) y ID ·RS (regiones neutras y contactos óhmicos).

En el primer párrafo de este apartado se dijo que la corriente del diodo no podía ser tan

alta como se quisiera. En caso contrario el dispositivo sufriría daños. Por ello no es práctica

aconsejable conectar directamente una fuente de tensión con los terminales del diodo. En todo

circuito real será necesario limitar el valor de la corriente que pueda circular por un diodo. Esto

4

La potencia que disipa el diodo es VD x ID. Por tanto, si ID es muy grande y el dispositivo no es capaz de transmitir al

exterior el exceso de calor, la temperatura será tan alta que éste puede destruirse.

16

puede ser realizado fácilmente conectando en serie con el diodo una resistencia con un valor no

muy pequeño tal y como se observa en la Figura 10.

A continuación haremos un estudio comparativo entre los modelos (a), (b) y (c)

representados en la Figura 9. Se analizó el circuito de la Figura 7 variando la fuente de tensión VS

entre -0.5 y 5V. En la Figura 11 se representan la corriente ID en función VS a partir de los

resultados obtenidos.

Ejemplo: Utilizando el modelo (a), la ecuación que hay que resolver para obtener VD en función de

VS, y a partir de ésta ID, viene dada por la Ecuación 2. No obstante, se procedió simulando el

circuito con SPICE. El modelo del diodo que se usó fue el más sencillo, especificando como único

parámetro la corriente inversa de saturación5 Io=1pA. En la simulación se utilizo una temperatura

de 25oC=298K. El fichero SPICE para la simulación del circuito rectificador es dado en la Tabla 1.

Figura 10. Efecto de la resistencia serie del diodo en polarización directa para dispositivos

reales.

5

Los valores de la constante de Boltzmann y de la carga del electron utilizados en el argumento de la exponencial de

(Ecuación 1)son k =1.38066 x 10-23J/K y q =1.60218 x 10-19C

17

Tabla 1. Código SPICE para la simulación del circuito rectificador.

.Simulación con diodo

VCC 1 0 DC 0

VD 1 2 0

R1 2 3 1K

D1 3 0 DIDEAL

.model DIDEAL D(Is=1p)

* ANALISIS DC

.DC vcc -0.5 +5 0.01

.PRINT DC I(VD)

.END

Para el circuito rectificador de media onda utilizando los modelos (b) y (c), el análisis se

hará en dos pasos. Primero se considerará que el diodo esté cortado. En tal caso, éste se comportará

como un circuito abierto (ID=0A), por lo que no habrá caída de tensión en la resistencia y la tensión

en el diodo será igual a la de la fuente (VD=VS). Como la tensión en el diodo no puede ser mayor

que la tensión umbral, cuando VS>VT, la tensión VD=VT y comenzará a circular corriente por R,

comenzando de esta manera a conducir el diodo. Por tanto, las ecuaciones que nos dan la corriente

por el diodo usando cualquiera de los dos modelos (b) o (c) son:

Ecuación 5

ID 0

V VT

ID S

R

si VS VT

si VS VT

La diferencia entre ambos modelos es la tensión umbral. En el modelo (b) VT =0 y en el

modelo (c) VT =0.6V (valor típico del silicio).

De los resultados representados en la Figura 11 se observa que los tres modelos son

equivalentes6 para tensiones negativas y positivas grandes. No obstante, el error relativo comienza

a destacar para valores positivos pequeños. Como cabría esperar, el modelo (c), que es más

complejo que el (b), da mejores resultados.

6

La diferencia de corriente entre el modelo (b) y (c) es constante e igual a VS /R-(VS-V )/R=0.6mA. Valor que resulta

despreciable cuando la corriente es grande

18

En la resolución del circuito que nos sirve como ejemplo, utilizando el modelo de la

Figura 9.(c), estando el diodo conduciendo, hemos asumido el valor de la tensión VD conocido e

igual a 0.6V. Conocida esta tensión, mediante la aplicación de las leyes de Kirchhoff al circuito

hemos calculado ID mediante la ecuación inferior de Ecuación 5. Este procedimiento da muy

buenos resultados con tensiones grandes. No obstante, debido al carácter exponencial de la

característica estática I-V del diodo, si intentamos calcular directamente el valor de la corriente ID

mediante la sustitución del valor aproximado VD = 0.6V en la ecuación Ecuación 1, EL ERROR

PUEDE SER CONSIDERABLE. Sirva como ejemplo el caso en que VS = 5V y aproximamos la

tensión umbral al valor 0.6V. El valor de la corriente predicho por el modelo (c) es ID = 4.4mA y los

valores obtenidos de evaluar la Ecuación 2 para la corriente y la tensión del diodo son 4.4293mA y

5.5706549V, respectivamente. Si intentásemos calcular ID sustituyendo VD = 0.6V en la Ecuación 1,

el valor obtenido para la corriente sería 14.033mA, es decir, un error relativo7 de 127%.

Figura 11. Corriente con los modelos (a) con I0=1pA, (b) con VT=0.6V, (c) con VT=0.6V

7

El error relativo se puede calcular mediante la expresión: 100x{Corriente del modelo (c)-Corriente del modelo (a)}/

Corriente del model (a)

19

Figura 12. Circuito rectificador y su representación equivalente cuando se usa el modelo (c)

del diodo.

1.3.3 Análisis en continua de circuitos con diodos

La principal diferencia entre los modelos aproximados del diodo dados en el apartado

anterior y el modelo más exacto dado en la Ecuación 1 es que éste último es un modelo de continua

genérico, es decir, es válido para cualquier valor de tensión entre los terminales del dispositivo. No

obstante, si en el análisis de un circuito utilizamos cualquiera de los tres modelos aproximados,

dependiendo de si el diodo está en directa o en inversa, tendremos que sustituirlo por un circuito

abierto o una fuente de tensión constante (con una resistencia en serie si procede). En general no se

puede determinar a priori si los diodos que forman parte de un circuito están en directa o en

inversa. Por tanto, a priori no sabremos por cuál de las dos opciones del modelo aproximado

sustituiremos los diodos. En general, el método de análisis que emplearemos será:

1. Hacer una suposición razonada del estado de cada diodo.

2. Dibujar el circuito sustituyendo los diodos conforme al estado supuesto en el punto anterior.

3. Mediante el análisis del circuito determinar la corriente en cada diodo en conducción y la

caída de tensión en cada circuito abierto que represente un diodo en corte.

4. Comprobar si las suposiciones hechas para cada diodo son correctas, es decir, si no se

incurre en ninguna contradicción. Entendemos por contradicción una corriente negativa en

un diodo en conducción o una tensión en el diodo cortado mayor que la tensión umbral.

5. Si hay contradicciones, los resultados obtenidos no son válidos y volvemos al punto 1

haciendo una nueva suposición sobre los estados de los diodos. Si no hemos incurrido en

20

ninguna contradicción validamos los resultados obtenidos dentro de las propias limitaciones

impuestas por el modelo usado. Si las tensiones que se manejan son grandes, cualquiera de

los modelos dará resultados aproximados a los valores del circuito real.

Para ilustrar como se aplica el método procederemos a analizar el circuito de la Figura

13.(a). El diodo del circuito estará en directa o cortado dependiendo de los valores de las tensiones

VA y VB. Pero como éstas no son conocidas procederemos según los pasos enunciados en el párrafo

anterior y utilizando el modelo de la Figura 9.(c) con VT =0.6V.

Supondremos inicialmente que el diodo está cortado y lo sustituimos por un circuito

abierto (Figura 13.(b)). En tal caso, como ID=0, por las resistencias de 2K y 8K circula la

misma corriente y el circuito de la izquierda se comporta como un divisor de tensión. Ahora es

inmediato comprobar que VA=VS ·8/10=16V. Aplicando la ley de Ohm al circuito de la derecha

obtenemos que VB = 10K ·1mA =10V. Como por la resistencia de 1K no circula corriente la

tensión entre sus terminales es cero y por tanto la caída de tensión en el diodo es VD=VA-VB=6V

V . Como esta tensión es mayor que la tensión umbral, el diodo no puede estar cortado y nuestra

suposición inicial fue errónea.

Sustituyendo el diodo por su modelo de conducción el circuito que tenemos que analizar

queda como en la Figura 13.(c). Aplicando la ley de Kirchhoff de las corrientes a los nudos A y B

obtenemos el conjunto de ecuaciones lineales que permiten resolver el circuito. Estas son8:

Ecuación 6

V A 20 V A V A VB 0.6

0

2

8

1

VB 0.6 V A VB

1 0

1

10

Resolviendo el sistema lineal de ecuaciones obtenemos: VA = 15.314V y VB = 14.286V.

Conocidos

estos

valores

podemos

calcular

la

corriente

que

circula

por

el

diodo

En la formulación de estas ecuaciones hemos tomado los valores de las resistencia en K y de las tensiones en V. Por

tanto, el valor de la fuente de corriente lo hemos tomado en mA

8

21

VA VB 0.6

428A . Como esta corriente es positiva el diodo está polarizado en directa y los

1K

resultados obtenidos son correctos.

Figura 13. Circuito utilizado como ejemplo para el análisis de circuitos con diodos.

1.4

CIRCUITOS RECTIFICADORES

1.4.1 Fundamentos de la rectificación

Todos los circuitos electrónicos se alimentan con tensiones continuas. Sin embargo, a la

mayoría de estos circuitos se le suministra la potencia que consumen a través de la red eléctrica. La

red eléctrica suministra tensiones alternas (que varía senoidalmente con el tiempo) de 50Hz a 220

voltios eficaces. Por tanto, es necesario convertir la tensión alterna, con una componente de tensión

continua (valor medio) igual a cero, en una tensión con componente de continua no nula. Esta

función la realizan los circuitos rectificadores, pudiendo éstos estar construidos únicamente con

diodos. Pero antes de presentar este tipo de circuitos definiremos algunos parámetros que

caracterizan a las señales eléctricas periódicas.

Supongamos que tenemos una fuente de tensión v(t) que es periódica y con el periodo

igual a T. Se define el valor medio como:

Ecuación 7. Valor medio.

v Vm

1 T

v(t ) dt

T 0

Para la tensión v(t) definida anteriormente se define el valor eficaz como:

22

Ecuación 8. Valor eficaz.

v 2 Veff

1

T

T

0

v 2 (t ) dt

Si bien el sentido del valor medio de una tensión periódica es bastante intuitivo,

intentemos darle sentido al valor eficaz. Supongamos que aplicamos la tensión v(t) entre los

terminales de una resistencia R. Como la tensión varía con el tiempo, la potencia que disipa la

resistencia es a su vez una función del tiempo de valor p(t)=v2(t)/R. A p(t) se le denomina potencia

instantánea. Si ahora quisiéramos conocer el valor medio de potencia consumida por R tendríamos

que evaluar la siguiente integral:

Ecuación 9

1

p Pm

T

T

0

1 1

p(t ) dt

R T

T

0

Veff

v (t ) dt

R

2

2

De la última igualdad podemos definir el valor eficaz como:

“El valor eficaz de una tensión periódica es el que debería tener una fuente de tensión

constante para que suministrara la misma potencia media a una resistencia cualquiera”

De igual manera que se ha definido el valor medio y eficaz para una tensión, pueden

definirse para una corriente. En este caso, la potencia media que disiparía una resistencia por la que

circulara una corriente periódica i(t) sería Ieff 2R.

Una forma de onda utilizada con profusión en ingeniería es la onda senoidal (por ejemplo

la de la red eléctrica). Esta puede representarse matemáticamente como v(t ) V p sen(

2

t ) ,

T

donde Vp es la amplitud o valor de pico y una constante que representa la fase. Variantes de esta

onda obtenidas mediante los circuitos de rectificación que estudiamos en este apartado, son las

versiones semirectificada y rectificada (Figura 14).

23

1

0

-1

0

50

100

150

200

250

300

350

0

50

100

150

200

250

300

350

0

50

100

150

200

250

300

350

1

0.5

0

1

0.5

0

Figura 14. Onda senoidal (arriba) y sus versiones rectificada (enmedio) y semirectificada

(abajo).

Tabla 2. Valores medios y eficaces de las ondas sinusoidales.

Vm

Veff

onda sinusoidal

semirectificada

rectificada

0

Vp/

2·Vp/

Vp/2

Vp/2

Vp/ 2

1.4.2 Circuito rectificador de media onda

El circuito rectificador de media onda fue ya utilizado (ver la sección 1.3.2) en la

discusión acerca de los modelos de gran señal del diodo para el análisis en continua. En este

apartado consideraremos que la fuente de tensión que excitaba aquel circuito variará con el tiempo.

No obstante, supondremos que el periodo T de la onda será suficientemente grande (o

recíprocamente, su frecuencia 1/T suficientemente pequeña) para que las capacidades internas del

diodo no surtan ningún efecto sobre el circuito. Por tanto, la característica estática del

semirectificador (es decir, la tensión de salida VO en función de la tensión de entrada VS) nos

permitirá realizar el análisis.

24

Figura 15. Circuito rectificador de media onda.

Como se observa en la Figura 15.(d), si despreciamos la resistencia interna Ron del diodo,

cuando VS sea mayor que la tensión umbral V, el diodo conducirá y Vo=VS -V. En caso que VS sea

menor que V, el diodo estará cortado, no circulará corriente por la resistencia y V0=0. Por tanto, la

característica estática del circuito es:

Ecuación 10. Característica estática del circuito semirectificador.

0

VO

VS VT

si VS VT

si VS VT

La Ecuación 10 se ha representado gráficamente en la Figura 15.(a) para dos valores de

tensión umbral, 0 y V . Como se puede ver en esta figura, para el caso de tensión umbral nula, en

los semiperiodos positivos de VS (curva b), el diodo conduce y VO = VS (curva c). Sin embargo, en

los semiperiodos negativos de VS, VO se hace cero. En general, para cualquier forma de la onda VS,

VO es una réplica exacta de ésta cuando sea mayor que VT y cero cuando sea negativa.

25

Amp. grande

Amp. pequeñ a

20

3

15

2

10

1

5

0

0

-5

-1

-10

-2

-15

-20

1

1.5

2

2.5

3

-3

1

1.5

2

2.5

3

Figura 16. Onda sinusoidal (trazo discontinuo) y versión semirectificada (trazo continuo)

para amplitudes grandes (20V) y pequeñas (3V).

Los resultados obtenidos con VT = 0 serán buenos siempre que el valor de pico VP de la

señal de entrada sea mucho mayor que unas décimas de voltio. En la Figura 16 se representa la

onda sinusoidal y su versión rectificada para una tensión umbral de 0.6V y dos valores de amplitud.

Si la amplitud es grande se observa que los semiperiodos positivos ambas curvas son prácticamente

iguales. En tal caso no importaría despreciar la tensión umbral (VT = 0). No obstante, si la amplitud

es pequeña las diferencias de las curvas en los semiperiodos positivos son considerables y el error

introducido por despreciar la tensión umbral (ello implica que los semiperiodos positivos son

iguales) sería a su vez considerable.

Cabe destacar dos aspectos importantes respecto de la onda semirectificada.

1. El valor máximo de la onda rectificada ya no es el valor de pico VP de la señal de entrada,

sino inferior e igual a VP –VT.

2. El intervalo de tiempo para el que la onda semirectificada es distinto de cero ya no es la

mitad del periodo (T/2) de la onda de entrada, sino inferior e igual a T/2-2· t1, donde

t1

V

T

arcsen( T )

2

VP

26

Para calcular t1 tenemos que considerar que este tiempo es el retraso en comenzar a

conducir el diodo desde que la onda de entrada cruza por cero con pendiente positiva. Por tanto, si

la tensión de entrada es un seno, despejando de VP sen(

2

t1 ) VT obtenemos t1

T

Los dos aspectos anteriores contribuyen a que el valor de continua de la señal rectificada

sea menor que el valor VP/ dado para el caso ideal en la Tabla 2. Por tanto el semirectificador

pierde prestaciones respecto del caso ideal VT =0. Hacemos notar también que cuando el diodo no

conduce debe soportar una tensión inversa igual al valor de pico VP de la tensión de entrada VS. Si

este valor fuera mayor que la tensión de ruptura en inversa del diodo, éste comenzaría a conducir y

no rectificaría. De toda la discusión argumentada en este párrafo podemos concluir diciendo que un

diodo rectificador es tanto mejor cuanto:

1. menor sea su tensión umbral VT

2. menor sea su corriente inversa de saturación Io

3. mayor sea la tensión inversa de ruptura BV

1.4.3 Circuito rectificador de onda completa

Con el circuito rectificador de media onda se puede pasar de una onda sinusoidal con valor

medio nulo a una onda semirectificada con valor medio VP/ . No obstante, si la onda resultante

fuera completamente rectificada, el valor medio se duplicaría (Tabla 2) para igual valor de pico de

la tensión de entrada.

En la Figura 17 se representa un circuito rectificador de onda completa. El subcircuito

constituido por los cuatro diodos recibe el nombre de puente de diodos y suele encontrarse en la

práctica integrado, es decir, todos los diodos fabricados sobre el mismo sustrato y con un único

encapsulado. Supuesto que las capacidades internas de los diodos son despreciables para la

frecuencia de trabajo, tal y como se hizo en el apartado 1.4.2, nos disponemos a calcular la

característica estática VS-V0 que posteriormente nos permitirá obtener gráficamente las ondas de

salida del circuito.

27

Figura 17. Circuito rectificador de onda completa y sus circuitos equivalentes cuando se

sustituyen los diodos por sus modelos ideales para tensiones de VS positivas y negativas.

Consideraremos que los diodo son ideales (VT = 0 y Ron = 0). Hacemos notar que en el

circuito el único elemento capaz de suministrar potencia es la fuente de tensión y la corriente

eléctrica debe salir de la fuente por el terminal cuya tensión es más positiva. Así pues, cuando VS es

positiva la corriente fluye de derecha a izquierda por la fuente y cuando llega al nudo A se

encuentra con dos diodos, D1 y D4. Evidentemente por D4 no puede derivarse ya que entonces,

éste estaría conduciendo en inversa. Por tanto, toda la corriente de la fuente se deriva por D1

(conduce). Cuando IS llega al nudo C se encuentra con D3, a través del cual no puede fluir puesto

que en tal caso, este diodo estaría conduciendo en inversa, y se deriva completamente por la

resistencia. Cuando la corriente llega al nudo D se encuentra con los ánodos de los diodos D2 y D4.

Pero como el cátodo de D4 se encuentra conectado al terminal positivo de la fuente y la caída de

tensión en la resistencia provoca que la tensión en el nudo D sea menor que en A, este diodo estará

cortado y la corriente retornará a la fuente de tensión a través del diodo D2, cerrándose el circuito.

Este situación se ha representado en la Figura 17.(b) donde los diodos D1 y D2, ambos en

conducción, se han sustituido por cortocircuitos, y los diodos D3 y D4, ambos cortados, se han

sustituido por circuitos abiertos. Como se observa en esta figura, VO=VS e IS=VS/R.

En caso que VS sea negativa se deja al alumno comprobar que la situación representada en

la Figura 17.(c) es correcta, donde D3 y D4 están conduciendo y D1 y D2 están cortados. Cabe

destacar que la corriente de nuevo circula a través de la resistencia desde su terminal superior al

inferior y que por tanto VO es de nuevo positiva, es decir, VO=-VS=|VS|.

La característica estática del circuito puede representarse matemáticamente como

28

Ecuación 11

V

VO S

VS

si VS 0

si VS 0

La Ecuación 11 nos dice que la salida del rectificador de onda completa coincide con la

del rectificador de media onda, cuando la tensión de entrada es positiva. Pero cuando esta última es

negativa, en los terminales de salida del rectificador de onda completa aparecerá la misma tensión

de entrada con signo positivo.

Se deja como ejercicio para el alumno, que en el caso de considerar una tensión umbral

mayor que cero, compruebe que la característica estática es

Ecuación 12. Característica estática de un puente de diodos

VS 2 VT

VO

0

V 2 V

T

S

si

VS 2 VT

si 2 VT VS 2 VT

si

VS 2 VT

reduciéndose la tensión de salida una cantidad equivalente a dos veces la tensión en

conducción de un diodo.

Por último, decir que la tensión mayor que tienen que soportar los diodos en inversa es el

valor de pico VP de la onda de entrada cuando VT =0 (VP –VT si VT >0).

1.5

CIRCUITOS RECTIFICADORES CON CONDENSADOR

Como se ha visto en las secciones anteriores, los circuitos rectificadores, en el caso ideal,

generan a partir de una onda con valor medio nulo, ondas semirectificadas o completamente

rectificadas de valor medio VP/ o 2VP/, respectivamente. El valor medio de las ondas rectificadas

puede ser aún mayor (próximo al valor de pico) si en paralelo con la resistencia se conecta un

condensador de gran valor.

Consideremos que en el circuito rectificador de la Figura 15 (d) conectamos en paralelo

con la resistencia un condensador, tal y como se ilustra en la Figura 18.

29

Figura 18. Circuito rectificador de media onda con condensador y formas de las ondas a la

entrada y a la salida.

Para el análisis de este circuito tendremos que considerar dos aspectos importantes:

1. Cuando el diodo conduce, ID es positiva, y el condensador se carga a través de éste. Como

la resistencia interna Ron del diodo es muy pequeña, la constante de carga c =RonC del

condensador es mucho menor que el periodo T de la fuente y podemos suponer que la

tensión del condensador es igual a la tensión en la fuente. Este se entiende fácilmente en el

caso de que el diodo fuera ideal. Entonces, éste se comportaría como un cortocircuito y para

todo instante de tiempo VC=VS (o en el caso que VT > 0 tendríamos VC=VS-VT).

2. Cuando el diodo está cortado, ID=0, y el condensador se descarga a través de la resistencia

R con una constante de tiempo d=R·C. Suponemos que d es mucho mayor que T,

descargándose el condensador más lentamente que la variación de la tensión en la fuente.

Para aclarar estos conceptos se recomienda al alumno que realice el siguiente ejercicio.

Ejercicio: Supuesto que la tensión VS de la Figura 18 es constante e igual a 5V, y que VC=0V en

t=0, obténgase la ecuación de carga del condensador utilizando para el diodo el modelo de la

Figura 9.(d).

(Nota: Compruebe previamente que el equivalente Thevenin del circuito entre los terminales a y b,

cuando el diodo conduce, es Vth Vs V

R

R

Vs V y Rth Ron

Ron

R Ron

( Ron R)

30

Supuesto que inicialmente el diodo está descargado, durante el intervalo temporal (0,T/4),

como la tensión en la fuente es positiva el diodo conduce. Además, como la constante de carga a

través del diodo es muy pequeña la tensión en el condensador es una réplica de la tensión en la

fuente. Ahora bien, en t=T/4 la tensión en la fuente comienza a decrecer con mayor rapidez que la

descarga del condensador a través de R, por lo que VC>VS y el diodo pasará a estar en corte. El

condensador se descargará con una evolución exponencial en el tiempo durante el intervalo (T/4, t1)

como en cualquier circuito R-C

vC (t ) VP e (t T / 4) / d ; T / 4 t t1

La descarga del condensador continuará hasta que el diodo comience a conducir de nuevo,

es decir, hasta que

Ecuación 13

v S (t1 ) vC (t1 ) VP sen(

2

t1 ) VP e (t1 T / 4) / d

T

A partir de t1 los procesos de carga y descarga del condensador se van sucediendo tal y

como se representa en la Figura 18.

El valor medio de la onda obtenida mediante este circuito, siempre que la constante de

descarga del condensador sea grande, es aproximadamente el valor de pico VP de la tensión en la

fuente y se puede calcular mediante la expresión:

VC

1

T

t3

t1

vC (t ) dt

t3

1 t2

2

t1 ) dt VP e (t t1 ) / d dt

t VP sen(

t

2

T 1

T

donde t1 es un valor ya conocido, t2=T+T/4 y t3 se obtiene por una ecuación simular a la

Ecuación 13, es decir,

v S (t 3 ) vC (t 3 ) VP sen(

2

t 3 ) V P e ( t 3 t 2 ) / d

T

En caso de utilizar un modelo del diodo más realista habría que tomar un valor para la

tensión umbral distinto de cero. En tal caso, la tensión máxima en el condensador ya no sería el

31

valor de pico de la tensión en la fuente, sino VP - V. Este hecho se ilustra en la Figura 19 obtenida

de la simulación en SPICE del circuito considerado. El fichero de entrada al simulador es dado en

la Tabla 3. El alumno puede comprobar que si sustituye en el fichero de comandos SPICE el valor

de la amplitud de la fuente por un valor más grande (por ejemplo 40) el efecto de tensión umbral no

nula del diodo es despreciable.

Tabla 3. Código SPICE para la simulación del circuito rectificador con condensador.

.Simulación del circuito semirectificador

VS 1 0 sin(0 4 50 0 0)

* El valor 4 es la amplitud de la fuente

D1 1 2 D1MODELO

Rl 2 0 1k

Cl 2 0 100u

.MODEL D1MODELO D(Is=1p)

* ANALISIS TRAN

.TRAN 0.1e-3 60e-3

.PRINT TRAN V(1) V(2)

.END

Figura 19. Formas de las ondas a la entrada y a la salida del circuito semirectificador con

condensador cuando se considera que un diodo real.

32

1.6

CIRCUITO REGULADOR CON DIODO ZENER

En el circuito de la Figura 15 se comprobó que el diodo, para valores de entrada VS

mayores que la tensión umbral, se comportaba como una fuente de tensión. Es decir, VD tomaba el

valor de tensión próxima a VT independientemente de la corriente que circule entre los terminales

del diodo. El inconveniente de utilizar este circuito como regulador de tensión9 es que la tensión

umbral de un diodo viene determinada por el tipo de semiconductor que se utilice en su fabricación

y por tanto, para un determinado material semiconductor, la tensión que suministra el circuito

siempre tomará aproximadamente el mismo valor (aproximadamente 0.6 V en silicio).

No obstante, si se utiliza un diodo Zener funcionando en su región de ruptura (Figura 20),

a través del diodo podrán derivarse corrientes comprendidas entre un valor mínimo (Iz,min) y un

valor máximo (Iz,max) sin que apenas varíe la tensión (Vz) entre sus terminales. A Vz se le llama

tensión Zener. El valor de la tensión Zener puede hacerse variar desde algunas décimas hasta

decenas de voltio dimensionando adecuadamente los parámetros de fabricación del diodo.

Figura 20. Característica estática del diodo Zener y circuito utilizado como regulador de

tensión.

9

Un circuito regulador es aquel que suministra una tensión constante frente a variaciones de la tensión de alimentación

y para diferentes valores de corriente de salida

33

El valor máximo de corriente que puede circular en inversa por el diodo viene limitado por

la potencia máxima (Pz,max) capaz de disipar el dispositivo. Ambos valores están relacionados

mediante la expresión

Ecuación 14. Potencia máxima capaz de disipar el diodo Zener.

Pz ,max V z I z ,max

Nótese en la Figura 20 que cuando la corriente en inversa del diodo es menor que Iz,min, la

pendiente de la curva es pequeña. Esto quiere decir que cambios en la corriente suponen cambios

en la tensión, no permaneciendo ésta constante. Por tanto, para que el diodo regule bien (mantenga

su tensión constante) es necesario que esté trabajando en la región a alta pendiente.

Para ilustrar esta discusión resolvamos un ejemplo numérico referido al circuito de la

Figura 20.

Ejemplo de regulador con diodo Zener:

Para los parámetros siguientes, calcular para que intervalo de valores de tensión VS el

diodo regula correctamente.

Datos: R=0.5K, RL=1K, Vz=10V, Iz,min=1mA y Pz,max=200mW.

Solución: De la Ecuación 14 sabemos que la corriente máxima que puede circular por el

diodo sin que éste se dañe es 20mA. Si aplicamos la ley de Kirchoff de las tensiones al circuito de

la Figura 20, teniendo en cuenta que la corriente que circula por R es Iz+ IL = Iz+Vz/RL, podemos

plantear la siguiente ecuación:

VS R ( I z I L ) Vz VS R I z Vz (1

R

)

RL

Si en esta ecuación sustituimos los valores máximo y mínimo de Iz obtenemos que:

15.5V Vs 25V

34

Según los resultados obtenidos, si la tensión en la fuente VS varía entre 15.5 y 25 voltios la

tensión en los terminales de la resistencia de carga RL permanecerá aproximadamente constante

entorno al valor Vz=10V. Para valores de tensión VS mayores de 25V el diodo correría el peligro de

fundirse al no ser capaz de disipar al exterior todo el calor generado por el efecto Joule y para

valores menores que 15.5V la tensión en RL ya no permanecería igual a 10V.

Figura 21. Regulador con diodo Zener excitado con la salida de un rectificador de media

onda.

El circuito regulador con diodo Zener puede utilizarse junto con el rectificador de media

onda con condensador para la alimentación con tensión constante de circuitos electrónicos que

consuman poca potencia. El circuito referido está representado en la Figura 21. La tensión de

entrada VS podría ser obtenida de la red eléctrica a través de un transformador. Mediante el diodo y

el condensador podría obtenerse la onda VC, que tal y como se muestra en la figura, tiene una alta

componente de continua. No obstante, el rizado (diferencia de tensión entre el valor máximo y el

35

valor mínimo) de esta onda puede resultar intolerable para la alimentación de circuitos electrónicos.

Ahora bien, mediante el circuito regulador (diodo Zener) el rizado disminuye considerablemente

(algunos milivoltios como valor típico) obteniéndose una tensión de alimentación casi constante.

En el circuito de la Figura 21 el condensador se descarga a través de la resistencia R, que a

su vez es la resistencia que limita la corriente que circula por el diodo Zener como en el circuito de

la Figura 20. Por tanto, la constante de descarga es d=R ·C. La resistencia Rp es una resistencia de

valor pequeño e igual a la resistencia de salida de la fuente de tensión VS. En caso que VS fuera

obtenida de la red eléctrica mediante un transformador, como la resistencia del secundario de éste

es pequeña, Rp podría eliminarse.

Ejemplo: Como obtener 10V de tensión continua a partir de la red eléctrica

Para obtener una tensión continua de salida de 10V desde la red eléctrica utilizando el

circuito de la Figura 21 se podría proceder como se detalla.

Elegiríamos un transformador reductor de 220V a 15V, ambos eficaces, para generar la

tensión alterna VS. De ésta manera el valor de pico de VS sería

2 15 =21.2V, un valor en el

intervalo de tensiones calculadas en el ejemplo anterior. De esta manera el diodo Zener regularía

correctamente10. Por tanto, para los valores usados en el ejemplo anterior, la tensión en RL sería

aproximadamente 10V.

1.7

DETECTOR DE ENVOLVENTE

En comunicaciones analógicas, una señal de alta frecuencia puede transportar información

útil usando la técnica llamada modulación de amplitud, conocida también por el acrónimo

anglosajón AM. De esta manera es posible transmitir información a grandes distancias utilizando el

espacio radioeléctrico. El ejemplo más significativo es la radio comercial en la banda de

10

Nótese que el valor máximo de la tensión VC sería aproximadamente 21.2-0.6=20.6V y por otro lado habría que

asegurarse que la constante de descarga del condensador fuera suficientemente grande para que el valor mínimo de VC

fuera mayor que 15.5V

36

frecuencias comprendida entre 540 y 1600KHz. Como su propio nombre indica, una señal11

modulada en amplitud se corresponde con una señal sinusoidal de alta frecuencia (en el intervalo de

frecuencias dado en este párrafo) cuya amplitud no es un valor constante, sino que varía

temporalmente. Matemáticamente:

Ecuación 15. Señal modulada en amplitud.

v AM (t ) VP (1 m vm (t )) sen(2 f p t )

En la Ecuación 15, VP es una constante con dimensiones de tensión, m es una constante

adimensional, positiva y menor que la unidad, llamada índice de modulación y fP es la frecuencia

portadora. La información que porta la señal vAM es la tensión vm(t), también llamada señal

moduladora, que toma valores en el intervalo (-1V,1V). En la realidad, la forma de vm(t) podría ser

una réplica exacta de la forma de una onda acústica, transformada en tensión eléctrica mediante un

transductor (micrófono). En la Figura 22 se representa una tensión AM cuando la señal moduladora

es un tono puro, es decir, vm(t)=sen(2 fm t), donde la frecuencia fm es mucho menor que fp. En ésta

misma figura se ha representado también la envolvente extraída mediante el detector que se explica

en este apartado.

Un detector de envolvente es un circuito electrónico que forma parte en un receptor de onda

media y cuya función es extraer la información de una señal AM, es decir, generar a partir de ésta

una tensión que sea una réplica de la envolvente. El detector de envolvente más sencillo se puede

construir usando un único diodo, con una topología idéntica al rectificador de media onda con

condensador estudiado en el apartado 1.4.2. Este circuito se ha representado de nuevo en la Figura

23.a.

11

Para ser precisos diremos que en el argot técnico por señal se entiende cualquier forma de onda que soporte

información. Puesto que la Ingeniería de Telecomunicación trata el procesado y transmisión de la información, a partir

de ahora hablaremos de señales y no de ondas, tal y como hemos hecho en los apartados anteriores, donde los circuitos

rectificadores se han utilizado para la conversión de energía alterna en continua.

37

15

10

5

0

-5

-10

-15

2.3

2.4

2.5

2.6

2.7

2.8

2.9

3

3.1

3.2

3.3

Figura 22. Señal modulada en amplitud vAM (trazo discontinua, fp=20 kHz y fm=1 kHz) y

señal a la salida de un detector de envolvente vC (trazo continuo).

Figura 23. El circuito detector de envolvente es representado en (a). En (b), al circuito

detector de envolvente se le ha añadido el subcircuito RL-Cb para filtrar la componente de

continua.

Supongamos que la señal vAM es una tensión modulada en amplitud por una tensión

sinusoidal, tal y como se representa en la Figura 22, donde las frecuencias portadora fp y

moduladora fm son 20Hz y 1Hz, respectivamente. Como ya se dijo en el apartado 1.4.2, cuando el

diodo conduce el condensador se carga a través de éste con una constante de tiempo c=Ron·C,

donde Ron es la resistencia en directa del diodo. Como Ron es muy pequeña, a su vez la constante de

38

carga del condensador es también pequeña. Por tanto, para que la tensión en el condensador sea

capaz de seguir a la tensión vAM, c debe ser mucho más pequeña que el periodo (Tp=1/fp) de la

señal portadora. Si esto es así, cuando la pendiente de la envolvente sea positiva se garantiza que la

tensión en el condensador seguirá a ésta. Este hecho se representa en la primera gráfica de la Figura

24 donde con línea continua se representa la tensión vAM(t) y con discontinua la tensión en el

condensador vC(t). Resaltamos que cuando vAM>vC + VT el diodo conduce y vC, al ser c<<Tp, es

capaz de seguir a vAM.

Ahora bien, cuando la pendiente de la envolvente es negativa, la tensión en el condensador

debe descargarse con suficiente rapidez. No obstante, como el diodo no puede conducir en inversa,

el condensador sólo puede descargarse a través de R1, con una constante de tiempo d=R1 C1. Para

garantizar que la descarga sea suficientemente rápida (en caso contrario ocurriría lo que se muestra

en la gráfica de la izquierda de la Figura 25 ) se debe verificar que d<<Tm, donde Tm es el periodo

de la señal moduladora (Tm=1/fm). Si se verifica esta condición ocurre lo que se muestra en la

gráfica de la Figura 22. Sin embargo, el valor de d no puede hacerse tan pequeño como se deseé.

Por ejemplo, si éste fuera del mismo orden o menor que Tp, en un semiperiodo de la señal portadora

el condensador se descargaría del todo y no mantendría el valor de la envolvente, tal y como se

ilustra en la gráfica de la derecha de la Figura 25. Por tanto la condición que debe verificar la

constante de descarga del condensador es:

Ecuación 16. Condición que debe verificar la constante de descarga del condensador

T p d Tm

Una solución de compromiso es asignarle a d el valor de la media geométrica de Tp y Tm,

es decir,

Ecuación 17. Valor recomendado de la constante de descarga

d T p Tm

39

16.5

16

15.5

15

14.5

14

13.5

13

12.5

12

2.15

2.2

2.25

2.3

2.35

2.4

Figura 24. Vista detallada de la Figura 22. La constate de carga c es suficientemente

pequeña para que la tensión vC (línea discontinua) sea capaz de seguir a la portadora cuando

el diodo conduce. La constate de descarga d es suficientemente pequeña para que el

condensador, al descargarse, sea capaz de seguir a la envolvente en los intervalos en los que

ésta tiene pendiente negativa. Con línea continua la señal AM.

En la Figura 23.(b) se representa el circuito detector de envolvente donde se han añadido

la resistencia RL y el condensador Cb. La función de estos elementos es eliminar la componente de

continua de la tensión vC(t). Si el condensador tiene un valor de capacidad alto se comportará,

aproximadamente, como una fuente de tensión constante, cuyo valor será el valor medio de vC. Por

tanto, la tensión en RL será vC vC , es decir, deja pasar a la resistencia sólo la componente de

alterna.

40

14

16

12

14

10

12

8

10

6

8

4

6

2

4

0

2

2.2

2.3

2.4

2.5

2.6

2.7

2.8

2.9

3

1.4

1.42

1.44

1.46

(a)

1.48

1.5

1.52

1.54

1.56

1.58

1.6

(b)

Figura 25. Efectos no deseados en el detector de envolvente. En (a), d es más grande que Tm y

el condensador no se descarga con suficiente rapidez. En (b), d es más pequeño que Tp en el

condensador se descarga completamente en los simiperiodos positivos.

20

15

10

5

0

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

5

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

5

10

5

0

-5

-10

Figura 26. Envolvente detectada. La gráfica de arriba es la tensión vC(t) en R1. La gráfica de

abajo es la tensión en RL después de restarle a vC(t) su valor medio.

41

Tabla 4. Código SPICE para la simulación del circuito detector de envolvente.

.Simulación del circuito detector de envolvente

*Generador de la onda AM

.SUBCKT generaAM 30

*Genera una senal AM con fp=455K y fm=10K

VCAR 10 0 SIN(0 10 455k)

RCAR 10 0 1

VMOD 20 0 SIN(1 0.7 10k)

RMOD 20 0 1

EAM 30 0 POLY(2) 10 0 20 0 0 0 0 0 1

RAM 30 0 1

.ENDS generaAM

*Modelo del diodo 1n4148. Hacemos notar que

Rs=16

.MODEL D1N4148 D(Is=0.1p Rs=16 CJO=2p

Tt=12n Bv=100 Ibv=0.1p)

*Circuito detector AM

XAM 1 generaAM

D1 1 2 D1N4148

RL 3 0 100k

C1 2 0 1.373n

R1 2 0 11k

CB 2 3 1u ic=8.005

.TRAN 0.01u 0.5m uic

.END

Ejemplo de diseño del circuito detector de envolvente:

Supongamos que queremos diseñar un detector de envolvente para aplicarlo a un circuito

receptor AM de la banda comercial. Si bien el intervalo de frecuencias que puede tomar la señal

portadora está comprendido entre 540 KHz y 1600 KHz, mediante un procesamiento previo

(realizado con un circuito llamado mezclador) la frecuencia portadora fp de la señal que ataca al

detector es 455 KHz. Si bien el oído humano es capaz de oír hasta 20 KHz, éste es un caso extremo.

Por tanto, es razonable elegir como frecuencia moduladora máxima de la señal recibida fm =10

KHz. Por tanto la constante de descarga d = R1 ·C1 la vamos a calcular como la media geométrica

de los valores inversos de ambas frecuencias:

42

d

1

14.82s .

f p fm

Supuesto que la resistencia serie del diodo sea Ron=16, como la constante de carga c

debe ser mucho más pequeña que Tp, eligiendo un valor 100 veces menor podemos calcular C1:

c Ron C1 0.01 T p C1 1.373nF

Conocido C1, a partir del valor calculado para d calculamos que R1=10.79K. Dando el

valor RL=100K (>>R1) y Cb=1 F, ya que estos deben ser grandes, acabamos el diseño.

Con estos valores, mediante simulación SPICE, hemos obtenido las curvas de la Figura 22

y la Figura 24. El fichero de entrada SPICE utilizado está escrito en la Tabla 4.

Al final del apartado 1.4.2 se enumeran las características que debe tener un diodo

rectificador. A diferencia de éste, un diodo utilizado en la detección de envolvente trabaja a niveles

bajos de tensión y potencia, no siendo la tensión de ruptura ni la potencia máxima capaz de disipar

parámetros críticos. Sin embargo, como en el ejemplo anterior, debe tener una respuesta buena a

altas frecuencias. A los diodos con muy buenas características a alta frecuencia se les llama

diodos de señal.

Una de las características de los circuitos detectores de envolvente es que manejan señales

de bajo voltaje, siendo un inconveniente la tensión umbral del diodo. En la práctica se pueden

construir circuitos rectificadores o detectores de envolvente, usando amplificadores operacionales

(circuitos que se estudiarán el curso próximo), que corrigen este defecto. El comportamiento de

estos circuitos es el mismo que los circuitos estudiados en el caso de que los diodos usados tuvieran

una tensión umbral nula.

43

1.8

EJERCICIOS RESUELTOS

1) En el circuito de la figura, el conmutador cambia de la posición inicial a la intermedia en el

instante t0 = 0, y a la posición final en el instante t1 = 10-2 s. Calcular la evolución de la tensión y la

corriente del condensador, vC(t) e iC(t), y la tensión del diodo, VD1, en función del tiempo.

Datos: vT = 0.7 V, vz = 1 V, vc(0) = 0 V

t0

1K

D1

t1

10 F

5V

Solución:

En el instante t0 = 0 el diodo queda polarizado directamente, ya que la fuente de 5 V

aparece conectada por el ánodo a través de una resistencia, mientras que el condensador,

descargado, está conectado directamente al cátodo. El circuito equivalente será:

1K

5V

0,7 V

10 F

Vc(t)

Planteando mallas se obtiene el siguiente sistema de ecuaciones

5 1 iC 0,7 vC

dvC

iC C

dt

y resolviéndolo obtenemos que

vC (t ) 4,3 0 4,3 e

t 0 ,1

da la evolución de la tensión del condensador en el tiempo. En general se tiene que

Vc(t)

44

vC (t ) v v0 v e

t

“es la tensión de cualquier condensador que pertenezca a una red RC que vea una

tensión constante entre sus extremos”

donde v0 0 V será la tensión del condensador en el instante inicial y v 5 0,7 4,3 V la

tensión a la que tendrá el condensador una vez alcanzado el régimen permanente. La

constante de tiempo característica del circuito valdrá R C 102 s .

La evolución del condensador vendrá dado por

vC (t ) 4,3 (1 e 10 t )V para t 0 t t1

2

Vc(t)

4,3 V

2,7 V

10 -2 s

t

Se puede observar que en cualquier carga o descarga exponencial, cuando t , la

tensión del condensador alcanza siempre el 63% del valor final V .

vC ( ) 0,63 4,3 2,7V

La tensión de la resistencia será

vR 5 0,7 vC 4,3 e 10 t V

2

y la corriente tanto de la resistencia como del condensador

iC iR

2

vR

4,3 e 10 t mA

R

45

“La corriente del condensador que forma parte de una red RC que ve una tensión

constante entre sus extremos también tiene la forma”

iC (t ) i i0 i e

t

En nuestro caso i 0 corresponde a la situación en la cual el condensador se encuentra

completamente cargado, e i0

5 0,7 VC (0)

4,3 mA sería la corriente inicial, cuando el

R

condensador está completamente descargado.

La tensión del diodo será vD1 0,7V

Cuando se alcanza el tiempo t1, el conmutador cambia nuevamente de posición. Como t1

coincide con , la tensión del condensador en el instante de cambio valdrá 2,7 V. Al ser

mayor que la tensión de ruptura del diodo, 1V, éste se encontrará polarizado en ruptura. El

circuito queda como en la siguiente figura.

1K

1V

10 F

Vc(t)

El condensador sigue perteneciendo a una red RC que ve una tensión constante entre sus

extremos (1 V), por lo que la solución general sigue siendo

vC (t ) v v0 v e

t

pero en este caso la tensión inicial del condensador será v0 2,7 y v 1

vC (t ) 1 1,7·e 10

2

t t1

V para t t1

46

Vc(t)

2,7 V

1V

10 -2 s

t

La corriente iR y la tensión vD1 del diodo será

iC 1,7 e 10 t mA

2

vD1 1V

47

1.9

EJERCICIOS PROPUESTOS

1) El circuito de la figura es excitado con la señal vE(t). Hallar:

a) Estado del diodo en t = 0.

b) Ecuación vC(t) en el intervalo [0,1ms].

c) Instante de conmutación del diodo.

d) Tensión vC(t) para t .

Datos: vT = 0 V (diodo ideal), vc(t=0) = 5V

20 K

A

D1

VE(t)

B

20 K

3V

70 nF

VE

2V

Vc(t)

0,5

t (ms)

2) Para la onda vS(t) de la figura, hallar

a) El valor medio de la tensión.

b) Valor eficaz de la tensión.

c) Valor pico a pico de la tensión.

d) Factor de rizado.

VS(t)

15 V

5V

0,5

1

t (ms)

-5 V

3) Si la onda vS(t) del apartado anterior es aplicada tal y como aparece en la siguiente figura, hallar

a) El valor medio de la tensión.

b) Valor eficaz de la tensión.

c) Valor pico a pico de la tensión.

d) Factor de rizado.

Datos: vT = 0.7 V

48

D1

VS

1K

Vc(t)

4) Si la onda vS(t) del apartado 2) es aplicada tal y como aparece en la figura, hallar

a) El valor medio de la tensión.

b) Valor eficaz de la tensión.

c) Valor pico a pico de la tensión.

d) Factor de rizado.

Datos: vT = 0.7 V

D1

VS

1 F

1K

VL(t)

5) Si la onda vS(t) del apartado 2) es aplicada tal y como aparece en la siguiente figura, hallar

a) El valor medio de la tensión.

b) Valor eficaz de la tensión.

c) Valor pico a pico de la tensión.

d) Factor de rizado.

Datos: vT = 0.7 V,vZ = 5V

D1

VS

1 F

0,9 K

0,1 K

Dz

VL(t)

6) Para el circuito de la figura hallar

a) Los estados de los diodos D1 y D2 en t = 0.

b) Los estados de los diodos D1 y D2 en t = .

c) El valor de tensión en el condensador para el cual D2 pasa de corte a conducción.

d) La evolución de la tensión del condensador vC(t) para t > 0.

Datos: vT = 0.6 V, vC(0) = 0

49

2K

D1

D2

20 V

1 F

VC(t)

1K

10 V

5K

7) Para el circuito de la figura hallar

a) El estado del diodo y la tensión del condensador en t = 0.

b) El estado del diodo y la tensión del condensador en t = .

c) El valor de tensión en el condensador para el cual el diodo cambia de estado.

d) La evolución de la tensión del condensador vC(t) para t > 0.

Datos: vT = 0.7 V, vC(0) = 0

1K

VC(t)

1 mF

t=0

D1

40 V

3K

19,3 V

8) Dado el circuito de la figura:

a) Hallar la función de transferencia v0 = f(vi)

b) Dibujar la corriente IR y la tensión VO, considerando que vi es la entrada que se indica.

c) Calcular el valor medio VDC, el valor de la tensión de pico a pico VPP, la tensión eficaz Vef y

el factor de rizado R de la tensión de salida VO.

Datos: VT = 0.7 V

10 K iR

10 V

D1

D2

Vi

0.25

Vo

0.75

1

t (ms)

7,3 V

5,3 V

0.5

-10 V

50

Resultados:

1)

a)

D1 off (vA = 0 V; vB = 5 V => vD1 < 0)

b)

vC (t ) 2 3·e

c)

d)

1,53 ms

2,5 V

a)

b)

c)

d)

vM = 5 V

vef = 11,18 V

vPP = 20 V

R = 400 %

a)

b)

c)

d)

vM = 7,15 V

vef = 10,11 V

vPP = 14,3 V

R = 200 %

t

1, 4·103

V

2)

3)

VS(t)

14,3 V

5V

0,5

1

t (ms)

-5 V

4)

VS(t)

a)

b)

c)

d)

vM = 12,87 V

vef = 12,91 V

vPP = 5,63 V

R = 43,74 %

14,3 V

8,67 V

5V

0,5

1

t (ms)

-5 V

5)

VS(t)

a)

b)

c)

d)

vM = 1,287 V

vef = 1,291 V

vPP = 0,563 V