CLASE4 - RTI (Real Time Interrupt) V20

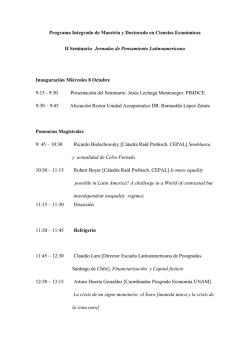

Laboratorio de microprocesadores Real Time Interrupt HC(S)12 10/08/2015 Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 1 RTI (HCS12) En en el desarrollo de software en tiempo real es necesario contar con una interrupción periódica. El motivo fundamental es que mediante una interrupción periódica podemos “muestrear” los eventos que genera el hardware evitandonos asi el gadfly loop y ademas limitar el numero de lineas de interrupcion dedicadas (recurso que puede ser escaso y dificil de administrar cuando el numero de interrupciones es grande). Todos los microcontroladores modernos poseen un generador periódico de interrupciones. Estos generadores pueden generar interrupciones periódicas a diferentes frecuencias programables por software. 10/08/2015 Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 2 RTI (HCS12) Antes de estudiar la RTI veamos de donde se obtiene el reloj que la alimenta. 16 MHz 10/08/2015 Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 3 RTI (HCS12X) PLL 80 MHz Nota: Synr [$34]=4 Refdv [$35]=1 10/08/2015 Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 4 RTI (HCS12) RTI Clock 80 MHz SCM: Self Clock Mode 40 MHz 16 MHz 16 MHz 10/08/2015 Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 5 RTI (HCS12) 16 MHz 10/08/2015 Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 6 RTI (HCS12) 16 MHz 10/08/2015 Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 7 RTI (HCS12) 10/08/2015 Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 8 RTI (HCS12) 10/08/2015 Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 9 Ejemplo RTI (HCS12) Divider Chain 16 MHz 1 1024 RTR[6:4]= 5 RTR[3:0]= 10 TRTI Si RTICTL=01011001b RTR[6:4]=5 (101) estamos dividiendo por 24 RTR[3:0]=9 (1001) Estamos dividiendo por 10 La cadena dividirá por: N= 1024 * 24 *10 = 210 24 10 = 10 214 (Ver Tabla) TRTI = (16MHz/N)-1 = 10.24 mseg Es decir que recibiremos una interrupción cada 10.24 mseg 10/08/2015 Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 10 RTI (HCS12) RTI IRQ CPU Interrupt Enable Vcc Clear Interrupt Flag 10/08/2015 D Q Interrupt Flag Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 11 RTI (HCS12) RTI IRQ CPU Interrupt Enable Vcc Clear Interrupt Flag 10/08/2015 D Q Interrupt Flag Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 12 Interrupciones (HCS12) Para borrar el RTIF hay que escribirle un “1” !!!! ´1´ 10/08/2015 Laboratorio de microprocesadores Ing. Claudio Muñoz- Ing. Daniel A. 13

© Copyright 2026