El Microblaze

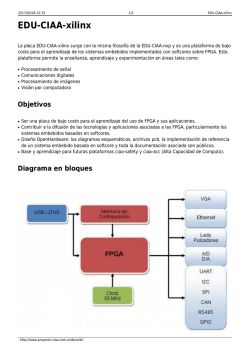

C l i c k t o a d d Procesador Microblaze The MicroBlaze™ embedded processor soft core y o u r t e x t Agenda 1 Introducción 2 Arquitectura MicroBlaze Introducción Introducción Procesadores Embebidos en FPGAs Diseños basados en la concurrencia de procesos donde se requiera capacidad de procesamiento, sin recurrir a un procesador externo. Introducción Soft vs Hard processors Soft Processor; El procesador se implementa simulando su comportamiento con un lenguaje de programación (HDL en el caso de Microblaze architecture Behavioral of procesador is … if ins_Entrada = Instrucción_Suma then acumulador <= dato1 + dato2; end if; … end; Introducción Soft vs Hard processors Hard Processor; El procesador es un circuito VLSI, con un diseño a nivel de transistor optimizado para ejecutar instrucciones en el mínimo tiempo posible. XILINX: SW_HW PowerPC IBM Virtex2Pro: 50% mas veloz que la opción SoftCore Introducción Microprocesadores Soft core: MicroBlaze •Versatilidad. •Tantos procesadores como capacidad tenga la FPGA. •Procesadores Personalizados ( Flash, UART, GPIO, etc.) Introducción Soft-processor Xilinx MicroBlaze: Microblaze es un soft processor descrito en VHDL Xilinx lo vende como un IP-core Herramienta muy potente para desarrollar proyectos relacionados con arquitecturas paralelas, codiseño, control y en toda investigación sobre software y estudio de metodologías de desarrollo. Optimizado para ejecutar códigoC. FPGA: Spartan y Virtex Introducción Soft-processor Xilinx MicroBlaze: FPGA => entre 14320 (Spartan II 15K) hasta 125.136 (Virtex II Pro 125) celdas lógicas MicroBlaze Soft Processor => alrededor de 2000 celdas lógicas El Microblaze Embedded soft RISC Processor Arquitectura RISC – Harvard – 32 Bits Soporte para sistemas operativos. Arquitectura Arquitectura Generalidades Todas las instrucciones toman un ciclo de reloj, excepto: Load y store (two clock cycles) Multiply (two clock cycles) Branches (three clock cycles, can be one clock cycle) Flujo HW-SW EDK-XILINX • Interfaz GUI - Xilinx Platform Studio (XPS) • Soporta MicroBlaze y PPC • Herramientas de desarrollo para especificacion de HW y SW • Xilinx Microprocessor Debug (XMD) • Board Support Package (BSP) • Perifericos IP (Parametrizable) • Herramintas GNU (Compilador, Debugger). Flujo - HW Flujo - SW IP cores Espacio de Memoria • Direcciones de 32 bits. • La cantidad de BRAM asignada es limitada. Arquitectura-Buses del Sistema E Buses El estandar IBM CoreConnect proporciona 3 buses para inteconectar Perifericos, Cores, y Logica personalizada. • • • Processor Local Bus (PLB) On-chip Peripheral Bus (OPB) Device Control Register (DCR) bus Buses BUS IPLB BUS DPLB Arquitectura-Buses del Sistema FSL (Fast Simple Link) Protocolo de comunicación que permite la comunicación con el periférico a través de sus propios registros internos. El periférico actua a modo de co-procesador y la conexión se realiza de manera sencilla a través de unos registros de desplazamiento de 32 bits de ancho. MicroBlaze soporta hasta 16 dispositivos conectados con este protocolo. Arquitectura-Pipeline Una arquitectura RISC aumenta fácilmente su rendimiento por medio de la segmentación (Pipeline). Solución arquitectónica para maximizar throughput (# datos procesados por segundo). (Hazards) son tratados por hardware Interrupciones El procesador tiene un solo puerto IRQ de interrupciones. • 4 ciclos de reloj de latencia • Disparada por nivel o flanco Si hay diferentes prioridades de interrupciones, necesitaremos un IP, que se encarga de multiplexar e identificar las diferentes fuentes de interrupción. • Aumento de la latencia de interrupciones • Manejo de interrupciones “torpe” • No hay interrupciones tipo wake-up • Pila de direcciones implementada por software. *Pagina 14 mb_rf_guide_10.1 FPU IEEE 754 Standard Single-Precision Floating Point ADD, SUB, MUL, DIV, Comp, Conv, SQRT Overflow returns signed 32-bit float 8-bit exponent, 23-bit mantissa Exceptions (when enabled) are regular Hardware Exceptions Result register not overwritten if exception TIPOS DE DATOS Bit-reversed big-endian • Word 32Bits • Half-Word Byte n Byte n+1 • Byte MSByte 0 MSBit Byte n+2 Byte n+3 LSByte 31 LSBit TIPOS DE DATOS Byte 8-bit, Short 16-bit, and Long 32-bit C-types: ‘char’ 8-bit ‘short’ 16-bit ‘long’ or ‘int’ 32-bit ‘float’ 32-bit SISTEMA EMBEBIDO EN FPGA

© Copyright 2026