estructura y tecnología de computadores - DAC

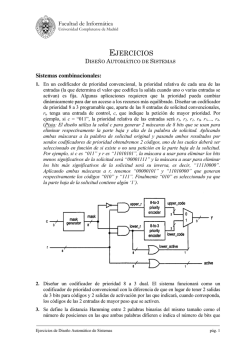

Universidad Rey Juan Carlos ESTRUCTURA Y TECNOLOGÍA DE COMPUTADORES Espacio de memoria principal Luis Rincón Córcoles Espacio de memoria principal Programa 1. 2. 3. 4. Mapa de memoria principal. Acceso a los datos en memoria principal. Configuración de la memoria principal. Conexión de los circuitos de memoria principal. 2 Espacio de memoria principal Bibliografía  P. DE MIGUEL. Fundamentos de los Computadores. 7ª edición. Paraninfo, 1999.  J.M. ANGULO, J.GARCÍA, I. ANGULO. Fundamentos y Estructura de Computadores. Paraninfo, 2003.  J.M. ANGULO, J.GARCÍA. Sistemas Digitales y Tecnología de Computadores. Paraninfo, 2002.  D.A. PATTERSON, J.L. HENNESSY. Estructura y Diseño de Computadores. Reverté, 2000.  DORMIDO, S. CANTO M.A., MIRA J., DELGADO A.E. Estructura y Tecnología de Computadores. 2ª edición. Sanz y Torres, 2000.  W. STALLINGS. Organización y Arquitectura de Computadores. 5ª edición, Prentice Hall, 2000. 3 Espacio de memoria principal 1. Mapa de memoria principal  Mapa de memoria de un computador: totalidad del espacio de memoria direccionable en el computador.  El tamaño del mapa de memoria depende del tamaño de las direcciones (de la anchura del bus de direcciones).  A menudo los computadores no tienen completamente lleno su mapa de memoria. 4 Espacio de memoria principal 2. Acceso a los datos en memoria principal  En un mapa de memoria, la unidad direccionable suele ser un octeto.  Sin embargo, la unidad accesible de memoria suele ser una palabra (16, 32 ó 64 bits). •Palabra de 16 bits: la memoria sólo admite direcciones con su último bit a 0. •Palabra de 32 bits: los dos últimos bits de la dirección están a 0. •Palabra de 64 bits: los tres últimos bits de la dirección están a 0.  Cuando se pretende acceder a unidades de información de tamaño menor que la palabra, hay que descartar los bits sobrantes mediante una red de alineamiento. •La red de alineamiento estará formada por multiplexores, desplazadores, circuitos de extensión de signo, registros auxiliares, etc.  Ejemplo: acceso a octeto con ancho de palabra de 32 bits. 5 Espacio de memoria principal Acceso a los datos en memoria principal  Organización de los datos de varios octetos: •Little endian: el octeto menos significativo primero. •Big endian: el octeto más significativo primero. Ejemplo: dato $12345678 en la posición $1000 de memoria en una memoria organizada en octetos. Little endian Big endian $1000 $78 $1000 $12 $1001 $56 $1001 $34 $1002 $34 $1002 $56 $1003 $12 $1003 $78  Para simplificar el diseño se suelen exigir accesos a memoria alineados a palabra. •Pueden quedar huecos desaprovechados entre variables si no ocupan el ancho de palabra completo. Ejemplo: dato de tamaño octeto entre dos datos de tamaño palabra, memoria alineada a palabra. Dato palabra 1, octeto 1 Dato palabra 1, octeto 2 Dato octeto Dato palabra 2, octeto 1 Dato palabra 2, octeto 2 6 Espacio de memoria principal Acceso a los datos en memoria principal  Admitir accesos no alineados disminuye el rendimiento, pues será preciso: •Acceder a dos palabras consecutivas para leer (o escribir) un dato de tamaño palabra no alineado. •Reordenar los bits leídos para componer el dato mediante una red de alineamiento.  Ejemplo: acceso a palabra de 32 bits no alineada. 7 Espacio de memoria principal 3. Configuración de la memoria principal  La longitud de las direcciones establece el mapa de memoria.  El ancho de palabra de la memoria establece el número de bits de cada dirección.  Al seleccionar la palabra buscada hay que decodificar la dirección para saber en qué chip de memoria se encuentra.  Los chips de memoria que se utilizan tienen un rango de direcciones y un ancho de palabra limitados. •Posiblemente habrá que utilizar varios chips de memoria para completar el tamaño deseado. •Será preciso completar los decodificadores de los chips para alcanzar el número de bits preciso para direccionar adecuadamente todas las palabras de la memoria. 8 Espacio de memoria principal Configuración de la memoria principal Ejemplo: mapa de memoria de 20 bits, memoria deseada de 128 Kpalabras de 16 bits, chips de 64 Kx1. Ejemplo: mapa de memoria de 16 bits, memoria deseada de 32 Kpalabras de 8 bits, chips de 8 Kx8. 9 Espacio de memoria principal 4. Conexión de la memoria principal  Señales de los chips de memoria: •Selección de chip: CS. •Habilitación de salida: OE. •Señal de lectura / escritura: R/W. •Selección de dirección de fila / columna en DRAM: RAS / CAS. •Bus de direcciones. •Bus de datos: de tipo triestado (puede haber líneas independientes para entrada y salida). 10 Espacio de memoria principal Conexión de la memoria: líneas de dirección  Para establecer las condiciones de decodificación se utiliza una lógica de selección de direcciones que determina qué rango de posiciones corresponde a cada fila de pastillas. 11 Espacio de memoria principal Decodificación incompleta  Se realiza cuando el mapa de memoria no está lleno. •Si se prescinde de los bits de dirección varias veces en el mapa de memoria.  Ejemplo: mapa de memoria de 20 bits, memoria deseada de 128 Kpalabras de 16 bits, chips de 64 Kx1. superiores, se repiten las filas de pastillas  Ejemplo: mapa de memoria de 16 bits, memoria deseada de 32 Kpalabras de 8 bits, chips de 8 Kx8. 12

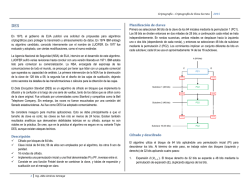

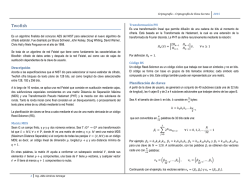

© Copyright 2026